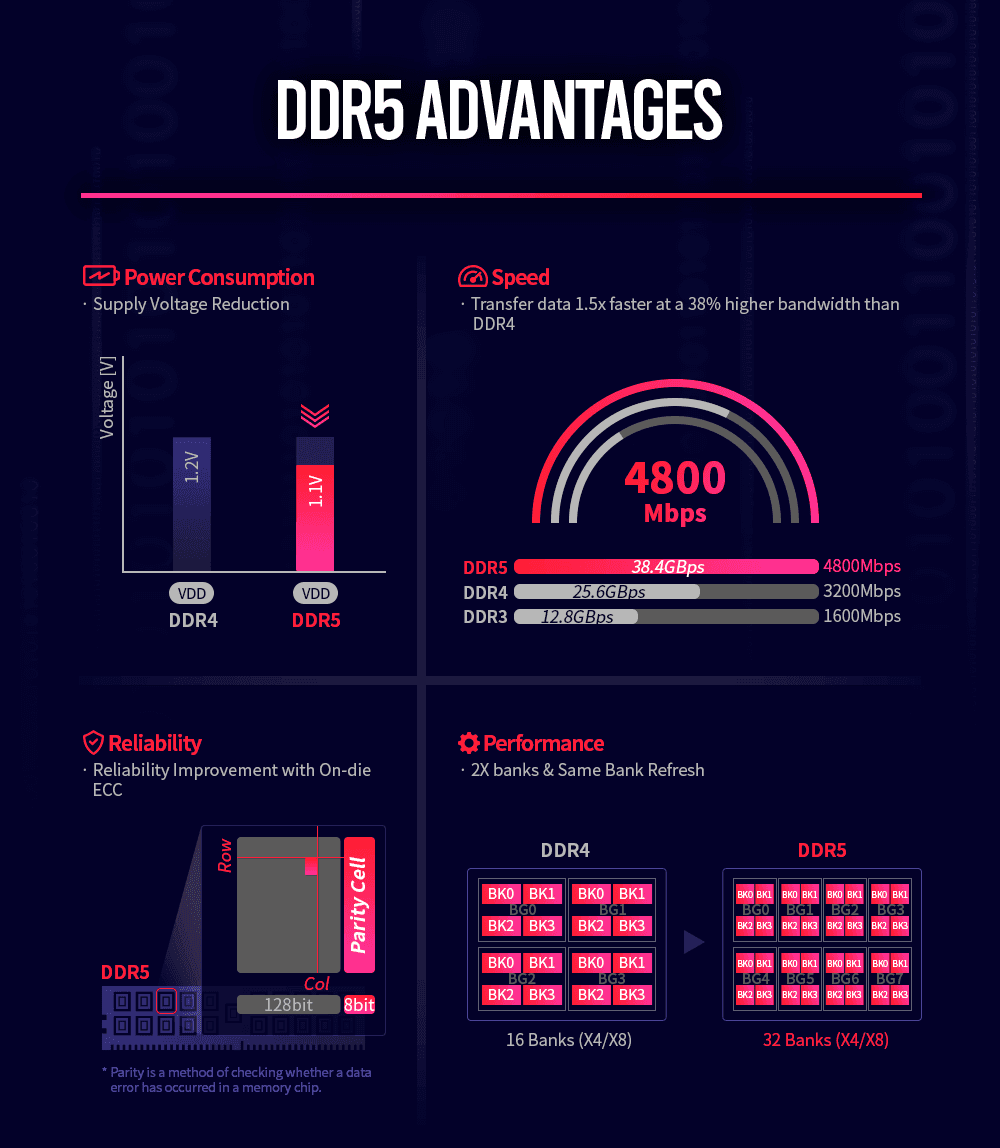

Tento týden jsme tu už měli jeden článek s informacemi o nových operačních pamětech DDR5, které by měly do PC přijít v letech 2021 až 2022. Ovšem prakticky vzápětí se vynořily důležité nové podrobnosti a navíc je jich o hodně větší balík. Kromě ostatních technikanálií a plánu vyškálovat rychlost eventuálně až na 8400 MHz je mezi nimi jedna možná úplně přelomová věc: DDR5 by zdí se mohla mít zabudovanou ochranu před chybami (ECC) přímo v základu. Možná je to šance, aby se po desetiletích dostala i do běžných počítačů, zatímco dnes jde o výsadu jen serverů a drahých pracovních stanic. K DDR5 se objevily informace od Hynixu a Micron publikoval blogposty a whitepaper, v nichž se rozepisuje o podrobnostech. DDR5 má v krátkosti přinést zlepšení spotřeby výkonu i spolehlivosti. Energetickou efektivitu má vylepšit snížení hlavního napájecího napětí z 1,2 V (standardní úroveň u DDR4) na 1,1 V, napětí VPP klesne z 2,5 V na 1,8 V. Na výkonu bude zapracováno přes značné množství dílčích změn, podle nichž to vypadá, že DDR5 bude mnohem větší převrat než DDR4.

DDR5 až na 8400 MHz?

Samotná přenosová rychlost bude (jak už jsme tu měli minule) v první generaci zřejmě 4800 MHz efektivně. Toto bude počáteční „výkonná rychlost“, ovšem DDR5 bude podporovat i nějaké pomalejší, protože ne všude je třeba maximální frekvence – nejnižší rychlost, se kterou se tedy bude dát setkat, by měla být 3200 MHz efektivně (DDR5-3200).

Další rychlostní stupně se pak jako obvykle budou přidávat postupně. Věděli jsme o DDR5-5200, DDR5-5600 a DDR5-6400, ale vypadá to, že cíle jdou ještě o dost dál. Hynix uvádí, že DDR5 by se měla dostat až na DDR5-8400, tedy efektivní přenosovou rychlost 8400 MHz (skutečné frekvence, s kterými rozhraní pracuje, takto vysoké ovšem nejsou).

Dvojnásobný prefetch, dvakrát více Bank Groups

To se ale bavíme o rychlosti samotného komunikačního rozhraní. V samotných pamětech DDR5, které sedí za ním, bude odpovídající navýšení propustnosti realizováno několika změnami. Prefetch bude dvojnásobný, místo 8n u DDR4 je v DDR5 použitý 16n – toto kopíruje změnu, která proběhla mezi GDDR5 a GDDR5X/GDDR6. Díky tomu se zdvojnásobí efektivní frekvence, zatímco reálně interní takt zůstane stejný. Burst Length bude místo 4 a 8 nově 16 a 32. Tato změna má dovolit nahrát v jednom kroku celou 64B cacheline, i pokud má procesor jen jednokanálový řadič paměti s jediným modulem DIMM.

Aby se při zvyšování hustoty pamětí (bajtů na čip) udržel výkon, bude zvýšeno množství banků v paměti. Uděláno je to pomocí zdvojnásobení počtu tzv. Bank Groups. V jednotlivé Bank Group budou stále čtyři banky jako v pamětech DDR4, ale standard DDR5 zdvojnásobí počet Bank Groups ze dvou či čtyř v DDR4 na čtyři nebo osm.

Toto umožní mít otevřených současně více stránek a zvyšuje šanci, že bude možné hned otevřít stránku, na kteoru zrovna z CPU přiběhne požadavek.

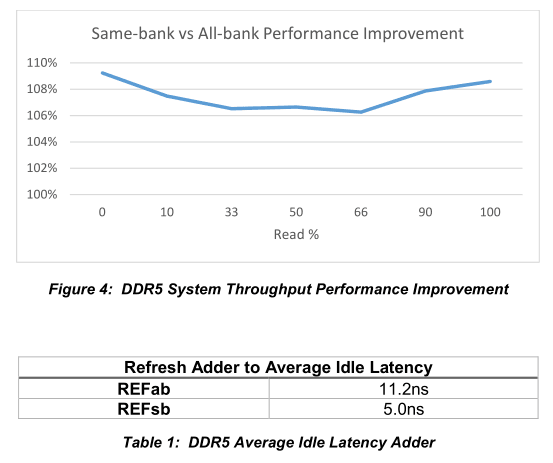

Další zlepšení výkonu by měly přinést změny v refreshi. DRAM potřebuje periodické obnovování, protože není nevolatilní a data v ní vydrží jen chvíli, takže musí být periodicky načtena a znovu zapsána. DDR5 přidává příkaz Refresh Same Bank (REFsb), který refreshuje jen jeden bank v každé Bank Group, oproti dosavadnímu příkazu REFab (Frefresh All Banks)

Protože pro refresh musí být banky nečinné a operace stojí nějaký čas, má refresh dopad na výkon. Pokud řadič pamětí bude používat místo REFab příkazy REFsb, mělo by se dát dosáhnout, aby potřebná obnovování celkem zabrala méně času a tím zmařila méně z potenciálního výkonu pamětí. Více času bude možné použít k přenosům, takže se zvedne efektivní propustnost.

Moduly tvořené dvěma kanály

Zdá se také, že paměťové moduly DIMM by v DDR5 mohly prodělat jednu architektonickou změnu, která by dále mohla zlepšovat výkon díky věším možnostem v paralelním přístupu. Není mi zatím úplně jasné, zda to tak bude vždy, nebo jenom volitelně, ale paměťový modul DIMM, který má dnes 64bitovou šířku, což tvoří v PC celý jeden kanál, by dle standardu DDR5 mohl být interně rozdělený na dva separátní kanály (šlo by o dvakrát 40 bitů).

Tyto kanály by mohly pracovat paralelně, byť jejich dílčí propustnost by pochopitelně byla asi poloviční. Se dvěma moduly a ekvivalentem dnešního dvoukanálového řadiče by tedy procesor vlastně využíval čtyři poloviční kanály. Toto by bylo podobné LPDDRx nebo GDDRx, kde má jeden kanál šířku 32 bitů. Výsledkem by zřejmě měl být vyšší reálně dosažený výkon proti modulům, které představují jediný kanál.

On-Die ECC: ochrana paměti přímo v čipech DDR5?

Že se zvyšuje výkon, jsme si tak nějak navykli. Ale DDR5 má zlepšit spolehlivost tím, že se ECC zdá se částečně dostane přímo do standardu, což by byl velký pokrok proti všem dosavadním generacím (DDR) SDRAM. Ochrana pamětí ECC je něco, co už dlouho existuje a je používáno v serverech. Dokáže opravit jeden vadný bit pomocí ECC algoritmu, nebo detekovat dvoubitové chyby. Toto je možná ještě důležitější, protože bez ECC náhodně nebo nějakým vlivem překlopené bity v RAM nejsou vůbec zjištěny a pokud se přihodí v nějakém datovém souboru, může pak být chyba permanentně zapsaná na disk a vaše data jsou pokažená, aniž byste o tom věděli. Detekce chyb je také důležitá k tomu, abyste zjistili, že je váš systém cílem útoku Rowhammer na RAM (proti kterému je ECC jednou dílčích z obran).

Pokud chcete dnes mít v počítači ECC paměť, musíte použít moduly, které mají na každých osm čipů DDR4 přidaný devátý, pomocí nějž se dosahuje redundance potřebná pro odhalení a korekci chyb. Tyto moduly mají tedy šířku 72 místo jen 64 bitů. Problém je, že běžné procesory a desky tyto ECC paměti nepodporují (výjimkou jsou částečně Ryzeny, které ECC neoficiálně podporují, ale i u nich to musí umět i základní deska a v tom už bývá problém).

Fungování On-Die Error Correction Code

U DDR5 má ale údajně být forma ECC přesunutá přímo do čipu samotného. Funkce On-Die ECC spočívá v tom, že přímo zápisy a čtení dat jsou chráněné paritní informací, která se ukládá do čipu spolu s daty. Řadič paměti pro každých 128 bitů zároveň do čipu zapíše i 8bitů paritní informace, celkově tedy 136 bitů. Při čtení z čipu se pak vrátí jak data, tak tato parity. Pro kontrolu je použité Hammingovo kódování. 8 bitů parity má stačit k detekování a také opravení jednobitové chyby v oněch 128 bitech dat. Pokud má chyba dva a více bitů, už není redundance dostatečná, pro ochranu proti dvoubitovým chybám bude nutno opět použít redundanci s čipem navíc jako nyní.

Součástí této technologie je i scrubbing ECS (Error Check and Scrub), tedy periodické kontrolování toho, zda u dat v paměti uložených sedí jejich parita a zda jsou tedy neporušená. ECS čte data z jednotlivých částí paměti a v případě detekce chyby je znovu uloží opravené. Může to automaticky dělat řadič paměti, který bude periodicky takto projíždět všechny adresy, nebo lze příkaz pro ECS používat manuálně. ECS hlásí počet odhalených chyb a také řádky s nejvyšším počtem chyb (což je asi pomůcka pro odhalování vadných modulů, nebo možná i útoku RowHammer).

Přítomnost ECC v čipech dává jisté šance, že ECC bude dostupnější. A že by ho konečně mohly mít i obyčejné moduly pro osobní počítače a notebooky, které jsou, jak už bylo řečeno, nyní nechráněné. Byl by to možná největší přínos DDR5 vůbec. Po obecném zavedení ECC se volá už hodně dlouho a je vlastně s podivem, v jakém masovém měřítku pořád v těchto pamětech přechováváme a zpracováváme data zcela bez ochrany a bez kontroly, zda v nich nedošlo k poškození (například cache v procesoru mají ECC už dlouho).

Chtěli byste mít v běžném osobním počítači nebo notebooku nějakou formu ECC ochrany pamětí?

Může se ECC konečně dostat i do běžných pamětí?

Nicméně to zní až moc dobře a zatím tedy s tímto asi nemůžeme počítat najisto. Nevíme, zda tato funkce třeba nebude volitelná, takže pak výrobci DRAM budu šetřit a pro PC budou zvlášť vyrábět čipy bez této On-Die ECC a buněk navíc pro paritní informaci. Nebo je možné, že ač budou moduly teoreticky toto umět, výrobci desek a procesorů budou přesto kašlat na podporu ve firmwaru, takže možnost použít toto ECC nebude využitá. Asi se mohou objevit i další komplikace, jinými slovy zatím není jisté, že tato novinka opravdu znamená „ECC pro všechny“, Žádný z výrobců DRAM také ve svých materiálech takový cíl neuvádí. Pokud by ECC bylo zabudované přímo ve všech čipech, sice by bylo dost divné ho nepoužívat, ale takto komplikovaně to už holt někdy chodí.

DDR5 nastoupí od roku 2021

Budeme tomu určitě držet palce, ale zatím tedy nezbývá než počkat na výsledek. Paměti DDR5 by měly být nasazovány od roku 2021 (někdy možná už letos, ale to asi budou výjimky a nebude se to týkat PC a x86 serverů).

Tip: Intel uvede DDR5 a PCI Express 5.0 roku 2021, v serverových procesorech Sapphire Rapids

Tip: Plány AMD v procesorech: Zen 4 už bude na 5 nm, přijde v roce 2022

Zdroje: Micron (1, 2, 3, 4), Hynix