Britská firma ARM Holdings (ovšem nyní vlastněná japonským SoftBank) pokračuje v rychlém vývoji svých CPU architektur určených zejména pro mobilní zařízení, ale nejen pro ně. Před dvěma roky uvedla firma Cortex-A73, loni Cortex-A75 a po roce přináší opět nový design procesorového jádra ve své highendové řadě: Cortex-A76. Ten má opět zvýšit IPC architektury a snad by mohl mít i ambice přiblížit se k výkonům, které nabízejí procesory x86 na PC. Teda alespoň podle marketingu firmy.

Jádro Cortex-A76 svým označením nevypadá moc nápadně, ale výkonem by mohlo poměrně vyčnívat. Předchozí Cortexy-A73 a A75 byly totiž architektury pocházející z linie jader zaměřené ne úplně na maximální výkon, ale spíše na efektivitu, což vede ke kompromisům. Do této linie patřil předtím ještě Cortex-A17. Vzdor názvu bude nové jádro „A76“ dost odlišné. Mělo by totiž patřit do linie výkonnějších a širších, byť méně efektivních jader, která se táhne od Cortexu A15 přes první 64bitový Cortex-A57 a poté Cortex-A72. Tato jádra pocházejí od vývojového týmu v Austinu, zatímco ona slabší a úspornější z francouzského týmu v Sophia/Antipolis u Nice.

Cortex-A76 přichází po delší odmlce Austinských jader a údajně jde o úplně novou od základu navrženou architekturu, která by proti poslednímu jádru A72 snad měla přinášet také slušný pokrok. Podle ARMU je Cortex-A76 jádro s výkonem „notebookové třídy“, ale stále s efektivitou mobilního SoC. Nicméně podobná tvrzení nejsou úplně vzácná, jak srovnatelný výkon skutečně bude, to se uvidí až v praxi. Mimochodem: toto jádro také obnáší také částečné odstranění 32bitové kompatibility – 32bitový kód (včetně instrukcí T32) bude již fungovat jen v neprivilegovaném uživatelském režimu, jádro a ovladače musí být vždy 64bitové.

Podle ARMu by Cortex-A76 měl umožnit až 35% zvýšení výkonu a až 40% zlepšení energetické efektivity. Toto srovnání ale není úplně mezi jablky a jablky a předpokládá použití lepších výrobních procesů. Čísla jsou pro hypotetický 7nm (TSMC) Cortex-A76 běžící na 3,0 GHz porovnaný jako s referencí s 2,8GHz Cortexem-A75 vyrobeným na 10nm procesu. Stále to ale naznačuje značné zlepšení IPC. Dle ARMu má výkon na 1 MHz dosahovat až 90 % výkonu dosahovaného architekturou Skylake od Intelu (a údajně při poloviční ploše a spotřebě) – tato architektura je ale stavěna na o dost vyšší takty, což je třeba brát v úvahu.

Podle ARMu by Cortex-A76 měl umožnit až 35% zvýšení výkonu a až 40% zlepšení energetické efektivity. Toto srovnání ale není úplně mezi jablky a jablky a předpokládá použití lepších výrobních procesů. Čísla jsou pro hypotetický 7nm (TSMC) Cortex-A76 běžící na 3,0 GHz porovnaný jako s referencí s 2,8GHz Cortexem-A75 vyrobeným na 10nm procesu. Stále to ale naznačuje značné zlepšení IPC. Dle ARMu má výkon na 1 MHz dosahovat až 90 % výkonu dosahovaného architekturou Skylake od Intelu (a údajně při poloviční ploše a spotřebě) – tato architektura je ale stavěna na o dost vyšší takty, což je třeba brát v úvahu.

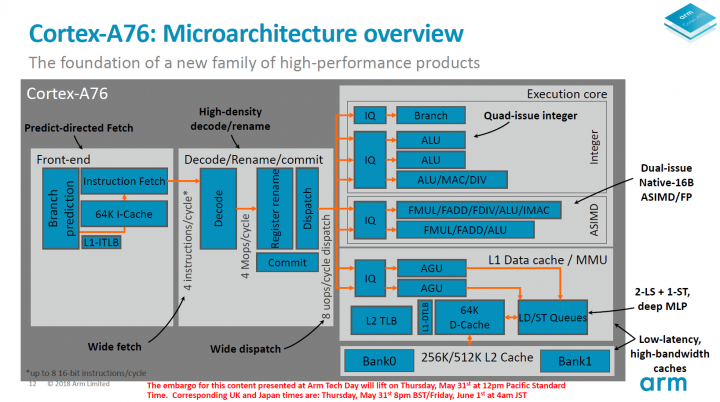

Architektura jádra Cortex-A76

Jako ostatní výkonná jádra ARM je nový Cortex-A76 navržen jako superskalární out-of-order architektura. Pipeline má 13 stupňů, některé se ale mohou překrývat, takže ARM uvádí, že jádro má latenci jako design s 11stupňovou pipeline. Jádro používá 16B fetch a obsahuje čtyři instrukční dekodéry – je tedy staveno na zpracování 4 instrukcí za jeden cyklus, neboli „4 issue“. Pro srovnání, architektury A73 a A75 měly dva, respektive tři dekodéry, takže zde došlo k významnému rozšíření, které může zvýšit IPC.

Zvláštností je, že prediktor větvení je předřazen fázi fetch a má dvojnásobnou kapacitu, až 32 bajtů. Dokáže tedy zpracovat 8 instrukcí a částečně zmírňovat prostoje při špatném odhadu. Dekodéry zpracovávají instrukce kódu na operace „macro-op“ (v některých případech na více než jednu), které se v následující fázi register rename ještě rozkládají na operace micro-op. Out-of-order optimalizace kódu pracuje s oknem (reorder bufferem) o 128 položkách, v rámci kterého může CPU instrukce přehazovat a z této fáze může odeslat ke zpracování ve výpočetních jednotkách až 8 micro-opů za cyklus.

Zvláštností je, že prediktor větvení je předřazen fázi fetch a má dvojnásobnou kapacitu, až 32 bajtů. Dokáže tedy zpracovat 8 instrukcí a částečně zmírňovat prostoje při špatném odhadu. Dekodéry zpracovávají instrukce kódu na operace „macro-op“ (v některých případech na více než jednu), které se v následující fázi register rename ještě rozkládají na operace micro-op. Out-of-order optimalizace kódu pracuje s oknem (reorder bufferem) o 128 položkách, v rámci kterého může CPU instrukce přehazovat a z této fáze může odeslat ke zpracování ve výpočetních jednotkách až 8 micro-opů za cyklus.

Toto out-of-order okno není ve srovnání s jinými architekturami příliš velké, například Intel má u Skylake hloubku 224 položek. Podle ARMu však zvětšování v simulacích vykazuje jen velmi malá zlepšení a tak bylo upřednostněno zachování nízké komplexity před potenciálním zvýšením výkonu. ARM totiž silně preferuje nízkou spotřebu a plochu jádra. Stejně to má asi i většina jeho zákazníků, výjimky by si možná mohly zaplatit změnu v rámci programu „Built on by ARM Cortex Technology“.

Výpočetní jednotky

Ačkoliv ARM slibuje velký nárůst IPC, není jádro ve skutečnosti tak široké, jako architektury Applu, Skylake, Zen nebo Exynos M3 od Samsungu. Už to bylo vidět u dekodérů, ale opakuje se to i u samotných výpočetních jednotek. Cortex-A76 obsahuje stále jen tři ALU, z nichž dvě podporují jednoduché aritmetické operace a jen třetí umí i komplexnější instrukce jako násobení, dělení nebo CRC (jejichž propustnost je tedy třetinová). Celočíselná část má pak ještě čtvrtou pipeline, která zpracovává větvení. Load/store jednotky jsou dvě.

Část FPU obsahuje dvě pipeline, které by měly mít pro SIMD instrukce Neon šířku 128 bitů (což je srovnatelné se SIMD jednotkami Zenu, který ale má jednotek víc; Intel má 256bitové jednotky a ve Skylake-X/SP s AVX-512 také 512bitové). Předchozí jádra měla ale jen 64bitové jednotky, takže toto znamená teoreticky aždvojnáosbný výkon v SIMD operacích, pokud nejsou limitované ničím jiným než samotnou FPU. Kromě toho ale ARM údajně jednotku SIMD/FPU posílil i jinak – operace mají zkrácené latence, takže v kódu s datovými závislostmi nebudou vznikat „bubliny“ a výkon může být vyšší. Například celočíselné SIMD násobení a jednoduchá floating-point aritmetika mají latenci sníženou ze tří cyklů na dva, floating point FMA z pěti na čtyři. Výkon SIMD ocení obecně například multimediální aplikace a také strojové učení – AI aplikace by moly být dokonce až 4× rychlejší díky novým dot product instrukcím.

Lepší paměťový subsystém

Jádro Cortex-A76 používá poměrně velké L1 cache – jak datová, tak instrukční mají kapacitu 64 KB se čtyřcestnou asociativitou. Latence je čtyři cykly, což je stejné jako u velkých jader Intelu nebo AMD, ARM se tedy nepokusil zvýšit IPC nižší latencí (za cenu možného snížení dosažitelných taktů). Datová propustnost je 2×32 bajtů za cyklus, u instrukční cache jen 32B/cyklus. Jádra pak mají dále privátní L2 cache opět s propustnosti 2×32B/cyklus, která může mít kapacitu 256 nebo 512 KB. U té je naopak latence agresivně snížená na pouhých 9 cyklů (pro srovnání – Zen má latenci 12 cyklů, Skylake 11). Počítá se také s L3 cache, která už je sdílená s dalšími jádry v klastru, jenž je propojen logikou ARM DynamIQ. Kapacita L3 může být 2–4 MB a latence 26–31 cyklů. V těchto parametrech si implementátoři mohou vybrat dle potřeby.

Kromě cache údajně ARM vylepšil také prefetchery které přednačítávají do mezipamětí data, aby se co nejčastěji předešlo situaci tzv. „cache-miss“, kdy čekání na data z operační paměti stojí mnoho desítek až stovky cyklů. Podle ARMu údajně propustnost při prací s pamětí v některých mikrobenchmarcích narostla až o 90 %, paměťový subsystém by tedy měl být robustnější. Právě jeho zlepšení by zřejmě měla dělat hodně z výkonnostních zlepšení jádra Cortex-A76, nicméně jejich realizace v praxi bude záviset na tom, zda paměťový subsystém správně implementuje výrobce finálního procesoru/SoC.

Kromě cache údajně ARM vylepšil také prefetchery které přednačítávají do mezipamětí data, aby se co nejčastěji předešlo situaci tzv. „cache-miss“, kdy čekání na data z operační paměti stojí mnoho desítek až stovky cyklů. Podle ARMu údajně propustnost při prací s pamětí v některých mikrobenchmarcích narostla až o 90 %, paměťový subsystém by tedy měl být robustnější. Právě jeho zlepšení by zřejmě měla dělat hodně z výkonnostních zlepšení jádra Cortex-A76, nicméně jejich realizace v praxi bude záviset na tom, zda paměťový subsystém správně implementuje výrobce finálního procesoru/SoC.

Nárůsty výkonu

IPC jádra má proti předchozímu Cortexu-A75 podle ARMU narůst až o 25 % pro celočíselný kód a až o 35 % tam, kde se silně využívá FPU nebo SIMD instrukce Neon. Už bylo také zmíněno „až“ 90 % zlepšení propustnosti pamětí, které ale pravděpodobně nemusí platit moc obecně. Jaké budou skutečné nárůsty výkonu ukáže až testování, zatím máme k dispozici jen odhady ARMu, u kterých je možná třeba s počítat s tím, že se uvádí hodnoty pro nejpříznivější výsledky, tedy zlepšení o 25 % může znamenat „až 25 %“. Podle ARMu by se údajně výkon při stejném taktu mohl v Geekbench zlepšit až o 28 % a v javascriptu až o 35 %.

ARM navíc počítá s tím, že A76 se bude typicky vyrábět na 7nm procesu, zatímco A75 na 10nm, a tím i s určitým zvýšením frekvencí. Oficiální srovnání výkonu (už ne IPC), která můžete vidět na následujících slajdech, pracují s jádrem A73 na 2,45 GHz, jádrem A75 na 2,8 GHz a A76 na 3,0 GHz; nicméně v mobilních zařízeních asi oba čipy typicky budou běžet níž. Proti 2,45Ghz Cortexu-A73 má 3GHz Cortex-A76 být rychlejší až o 90 % v celočíselných a o 150 % rychlejší ve floating-point operacích, celkové skóre v benchmarku Geekbench má být lepší o 80 %. rozdíl proti Cortexu-A75 je menší, celkově ARM slibuje 35 % navíc.

Cortex-A76 by přitom podle ARMu mohl mít ještě na víc. Mimo mobily a s vyšším TDP by údajně pro špičkový jednovláknový výkon mohlo jádro běžet až na 3,3 GHz, to už by ale bylo při spotřebě několik wattů. Naopak pokud se bude hledět na efektivitu, má Cortex-A76 být při stejných 750 mW příkonu být až o 40 % výkonnější než Cortex-A75, nebo až o polovinu méně žravý při stejném výkonu. Ovšem opět jde o srovnání 10nm a 7nm implementace a lze čekat, že většina tohoto zlepšení zde bude dána právě procesem.

Reálně na trhu nejdřív za rok

Jak už to u licenčních jader ARM chodí, tuto novinku je třeba brát v budoucím kontextu. Odhalení je zatím jen na papíře, reálně se tato jádra začnou na trhu objevovat tak za jeden až dva roky. Mezi prvními by je asi mohlo nasadit Huawei v čipech HiSilicon Kirin a Qualcomm v Snapdragonech (za předpokladu, že se překvapivě nevrátí k vlastní architektuře). Zároveň by ale měl ARM pokračovat v rychlé kadenci uvádění inkrementálních vylepšených návrhů. Na Cortexu-A76 budou tedy stavět pozdější vylepšení následníci.