Poslední dny se zájemcům o architektury CPU dostávalo štědrých dávek novinek, když Intel odhalil obě architektury v nových procesorech Alder Lake: velké jádro Golden Cove (což bude zatím nejvýkonnější x86 jádro) a menší Gracemont (které je prý zase nejúspornější). Něco teď ale máme i od konkurence. Na svět začínají vyplouvat první údaje o architektuře Zen 4, kterou budou používat za zhruba rok 5nm procesory Ryzen.

Zdrojem těchto informací je onen hack serverů Gigabyte, z kterého pocházejí také schémata platformy AM5, o nichž jsme psali v pondělí. V dokumentech, které hackeři zveřejnili (vedle toho, že Gigabyte vydírají o výpalné hrozbou, že zveřejní vše), jsou zdá se i informace, z kterých se dá něco vyčíst o vlastnostech Zenu 4. Jde jenom o částečné charakteristiky, protože nějaký celkový přehled jádra nemá AMD důvod touto cestou sdílet, ale lepší než nic.

L2 Cache zvětšená na 1 MB

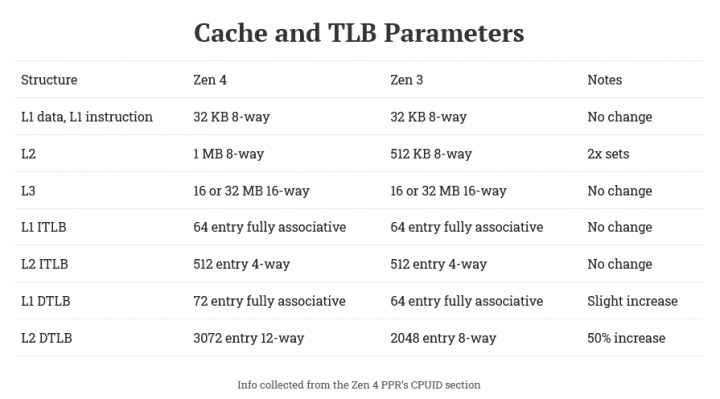

První věc, která se v dokumentech našla, jsou informace o pamětech cache a některých dalších souvisejících parametrech. L1 cache procesoru bude bohužel bez zvýšení kapacity – AMD i na 5nm procesu ponechá datovou i instrukční L1 na 32 KB s osmicestnou asociativitou. U datové L1 cache se ale změnil alignment, zarovnání bude na 64 bajtů, zatímco předchozí jádra Zen až Zen 3 používala 32bajtové.

Ale AMD poprvé od prvního Zenu zvětší L2 cache. Podle dokumentů má Zen 4 nově 1MB L2 cache, byť asociativita zůstala nezměněná (osmicestná). Alder Lake/Golden Cove proti tomu má 1,25 MB o 10cestné asociativitě. Zatím není známo, zda se zvětšením cache zhorší její latence, která je u Zenu až Zenu 3 12 cyklů (s výjimkou Ryzenů 1000, kde původní revize čipu měla asi kvůli errata prodlouženou latenci na 17 cyklů).

Translation Lookaside Buffery projdou ale změnami, které by mohly zlepšit výkon práce s pamětí i IPC. L1 a L2 TLB pro instrukce se nemění, ale TLB pro data ano: L1 TLB pro data se zvětší ze 64 na 72 položek (má plnou asociativitu). A zejména se o 50 % zvětší L2 TLB pro data, z 2048 položek s 8cestnou asociativitou na 3072 s 12cestnou asociativitou.

Větší L2 cache a změny v TLB by mohly zvýšit IPC jádra Zen 4, ovšem asi to bude záviset i od toho, zda se zvětší latence a zde se třeba nějak nezmění něco dalšího (u Tiger Lake například 1,25MB L2 cache zdá se nepřinesla o výrazně lepší výkon, než podávala 512KB v Ice Lake a Rocket Lake, nebo aspoň ne v průměru).

Je ale pravděpodobné, že spolu s těmito dokumentovanými změnami budou v Zenu 4 provedené i další úpravy a zvětšení struktur, které by mohly IPC zvýšit. Například by se nabízelo, aby AMD konečně výrazně zvětšilo Re-Order Buffer, jehož 256 položek je poměrně malá kapacita na tak výkonné jádro (stejnou kapacitu má teď „malé“ jádro Intelu Gracemont, velké Golden Cove má 512 položek). Ovšem dokumenty zatím tyto změny neukazují.

Jen čtyři ALU. Bude IPC nižší než u Intel Golden Cove?

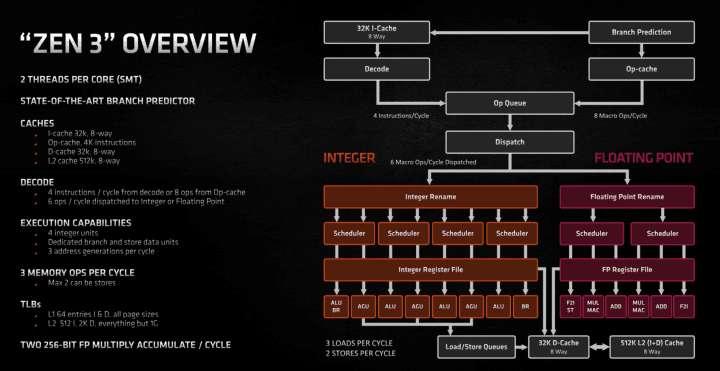

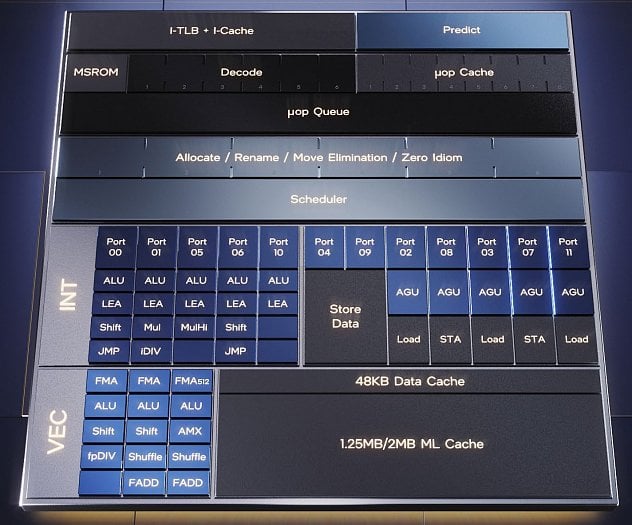

Na druhou stranu se zdá, že Zen 4 nebude zvětšovat šířku jádra (což dělá Golden Cove) a bude spíše vylepšovat evolučně další parametry. Cíl asi bude laděním dostat větší IPC ze struktur, které byly přidány v Zenu 3. Podle webu Chips And Cheese, který na tyto uniklé informace upozorňuje, totiž dokumentace popisující performance countery naznačuje, že jádro Zen 4 zůstane u čtyř schedulerů v celočíselné části tak, jak to má Zen 3. V tom je na každém scheduleru napojená dvojice jednotek (po jedné ALU a AGU, jen u čtvrtého scheduler je to ALU a jednotka pro větvení).

Při zachování těchto čtyř schedulerů asi proto není prostor pro přidání dalších výpočetních jednotek, ani load/store jednotek. Zen 4 podle tohoto zřejmě pořád bude mít čtyři ALU. Uvidíme tedy, jak velký nárůst IPC se AMD podaří zrealizovat, možná by ale tentokrát mohl být nižší, než jaký přinesl Zen 3 proti Zenu 2. Intel tak možná bude mít šanci udržet si svými procesory Alder Lake a Raptor Lake prvenství v jednovláknovém výkonu, protože pravděpodobně bude mít výhodu vyšších frekvencí a podle tohohle by možná ještě mohl mít i vyšší IPC než Zen 4.

Schéma CPU jádra Golden Cove ve verzi pro PC procesory Alder Lake ukazuje pět ALU a pět AGU, zatímco Zen 4 by mohl mít stále čtyři ALU a tři AGU (Zdroj: Intel)

Schéma CPU jádra Golden Cove ve verzi pro PC procesory Alder Lake ukazuje pět ALU a pět AGU, zatímco Zen 4 by mohl mít stále čtyři ALU a tři AGU (Zdroj: Intel)I když toto je zatím jen spekulace, teprve uvidíme, co se AMD podaří z architektury se čtyřmi ALU vydupat. Možná je v tomto designu ještě pořád dost nevyužitého potenciálu.

AVX-512: podpora na stejné úrovni, jako Ice Lake-SP?

O tom, že Zen 4 bude umět 512bitové instrukce AVX-512 (které paradoxně Intel zapíchnul u desktopových a notebookových procesorů Alder Lake), už jsme se dozvěděli před nějakou dobou. Uniklé/ukradené dokumenty to jen potvrzují. A navíc už i ukazují, která všechna rozšíření má AMD podporovat. Zen 4 má podle nich umět prakticky všechny subsety, které mají 10nm procesory Intel Ice Lake-SP pro servery.

Podporované je AVX-512F (základní 512bitová sada) a dále rozšiřující subsety VL, BW, CD, IFMA, DQ, VPOPCNTDQ, BITALG, VNNI (poměrně užitečný pro umělou inteligenci), VBMI, VBMI2 a také podpora výpočtů s hodnotami BFloat16, což je užitečné pro trénování neuronových sítí. Snad by také mělo být podporováno rozšíření GFNI (Galois Field New Instructions).

Z pohledu kompatibility tedy bude podpora AVX-512 na velmi vysoké úrovni. Otazník ale zůstává nad výkonem, kde není jasné, zda bude mít Zen 4 skutečně plně 512bitové jednotky, nebo zda bude používat existující 256bitové jednotky spřažené po dvou nebo s vykonáváním ve dvou cyklech. Podle dokumentace zřejmě v Zenu 4 mohou některé μOPy přistupovat k datům o šířce až 64 bajtů, což by odpovídalo 512bitovému vektoru.

To by napovídalo, že 512bitové instrukce by mohly být dekódovány do jednoho μOPu a tedy vykonávány v jednom taktu (vykonávání ve dvou taktech generuje dva separátní μOPy). Ale neznamená to, že to platí pro všechny instrukce. Mohlo by třeba jít jen o některé speciální operace, zatímco většina by se dělila. Pravděpodobnější asi je, že Zen 4 bude mít spíše omezený výkon v AVX-512, kdy se na zpracování jednoho 512bitového vektoru spojí dvě 256bitové FPU pipeline. Operace floating-point FMA v šířce 512 bitů bude pravděpodobně podporovat jen jednou za cyklus.

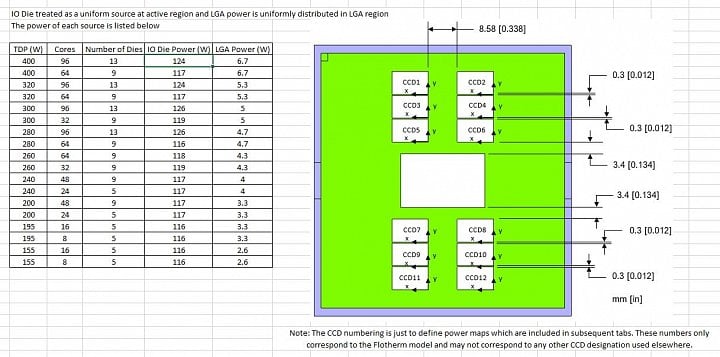

5nm čiplet s jádry Zen 4 je lehce menší, než 7nm čiplet se Zenem 2

Z dokumentů ukradených z Gigabyte zřejmě také známe velikost čipletů Zenu . Mají mít rozměr 10,7 × 6,75 mm (72,2 mm²), což by znamenalo, že jsou menší (a tím hůř chladitelné), než u Zenu 3. Dokonce jsou i o trošku menší než u Zenu 2 (u toho má jeden CPU čiplet 74 mm²), ale už ne o moc. Rozměr IO čipletu procesorů do socketu AM5 neznáme, ale IO čiplet pro Epyc 7004 Genoa je údajně 397 mm².

Flashování BIOSu z USB klíčenky bude integrované do procesoru, mohly by ho umět prakticky všechny AM5 desky

Zajímavá novinka je, že na platformě AM5 by mohla být přímo do procesoru Ryzen zabudovaná schopnost aktualizovat BIOS desky z portu USB (respektive z klíčenky připojené na něj), jelikož křemík bude obsahovat mikrořadič, který flashování BIOSu zajistí (asi i když CPU jinak nebude fungovat). Nahrávání BIOSu se spustí aktivací konkrétního GPIO pinu procesoru, bude stačit, aby na něj na desce bylo napojené tlačítko nebo aspoň dva piny pro nasazení jumperu.

Schéma konektivity platformy AMD AM5. Všimněte si portu USB pro update BIOSu, napojeného přímo na procesor (Zdroj: VideoCardz)

Schéma konektivity platformy AMD AM5. Všimněte si portu USB pro update BIOSu, napojeného přímo na procesor (Zdroj: VideoCardz)Toto by mohlo skoro úplně vyřešit problémy kompatibility nových procesorů se staršími deskami, kdy se při vydání CPU muselo řešit, zda už má deska dost nový BIOS, nebo jak ji updatovat, pokud nemáte po ruce starší CPU. Funkce aktualizace BIOSu z USB portu se sice na deskách už beztak dost rozmohla, ale díky integrování do CPU by ji nyní mohly mít už prakticky všechny desky včetně těch nejlevnějších.

Tip: 5nm procesory AMD Zen 4: Epyc Genoa má 13 čipletů a 96 jader, v desktopu víc jader nebude

Storage Class Memory pro 5nm Epyc

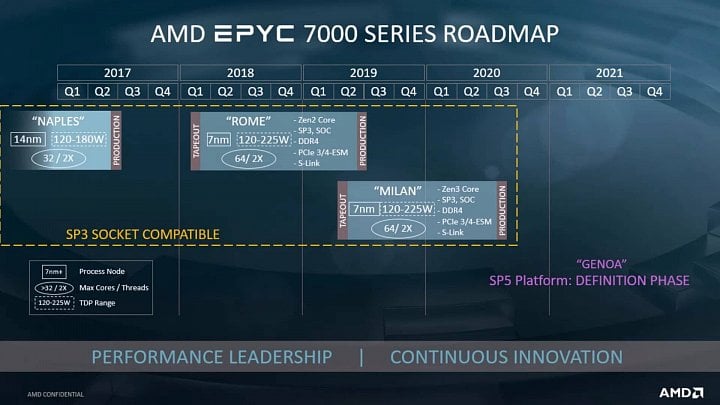

Článek Chips and Cheese jde do detailu i u serverové verze Zenu 4 (Epyc Genoa), kde však jde o pro nás asi celkem odtažité detaily. Možná ale stojí za to zmínit, že specifikace AMD počítají s tím, že tyto procesory budou podporovat „Storage Class Memory“ (SCM), tedy nevolatilní paměti podobné jako Intel Optane DC Persistent Memory. Ovšem tato SCM asi může být založená na NAND Flash a ne na pamětech 3D Xpoint, protože Micron ohlásil, že s nimi končí. A ty od Intelu se asi nedají očekávat.

Dokumenty také potvrzují dřívější zprávy, že Epyc Genoa bude mít 12kanálový řadič DDR5, až 96 jader a oficiálně podporovaná frekvence má být u těchto procesorů DDR5-5200. Také ale zdá se mohou stoupnout TDP. U 96jádrových modelů AMD zdá se počítá s 280W modely jako dnes, ale mají existovat také výkonnější verze s TDP až 400 W (AMD tak dorovná brutální 400W Xeony „Advanced Performance“). Je možné, že ty budou pro vodou chlazené HPC stroje, ale AMD evidentně také nebude stát stranou, když trh serverových komponent směřuje obecně k vyšší energetická (a tepelné) hustotě serverů...

Galerie: Uniklé či zveřejněné dokumenty k architektuře AMD Zen 4

Zdroje: Chips and Cheese, KittyYYuko