Pokud mi něco neuniklo, byla to Toshiba, kdo jako první přišel s myšlenkou přijít po NAND typu TLC – která sama tou dobou vypadala už poněkud problematicky, než se to po příchodu 3D NAND hodně zlepšilo – s ještě choulostivější verzí QLC NAND, která uchovává v každé buňce čtyři bity místo tří, a musí proto rozpoznávat dvojnásobek úrovní napětí (16 místo 8). Momentálně to vypadá, že se QLC podařilo dostatečně zvládnout, což je možná důvod, proč teď Toshiba opět hodlá zajít dál. Firma nyní odhalila plány na PLC NAND, tedy další úroveň s už 5bitovým záznamem do jedné buňky, a tím opět horší životností a potenciálně i výkonem.

PLC NAND už funguje. Zatím ale není jasné, kdy přijde

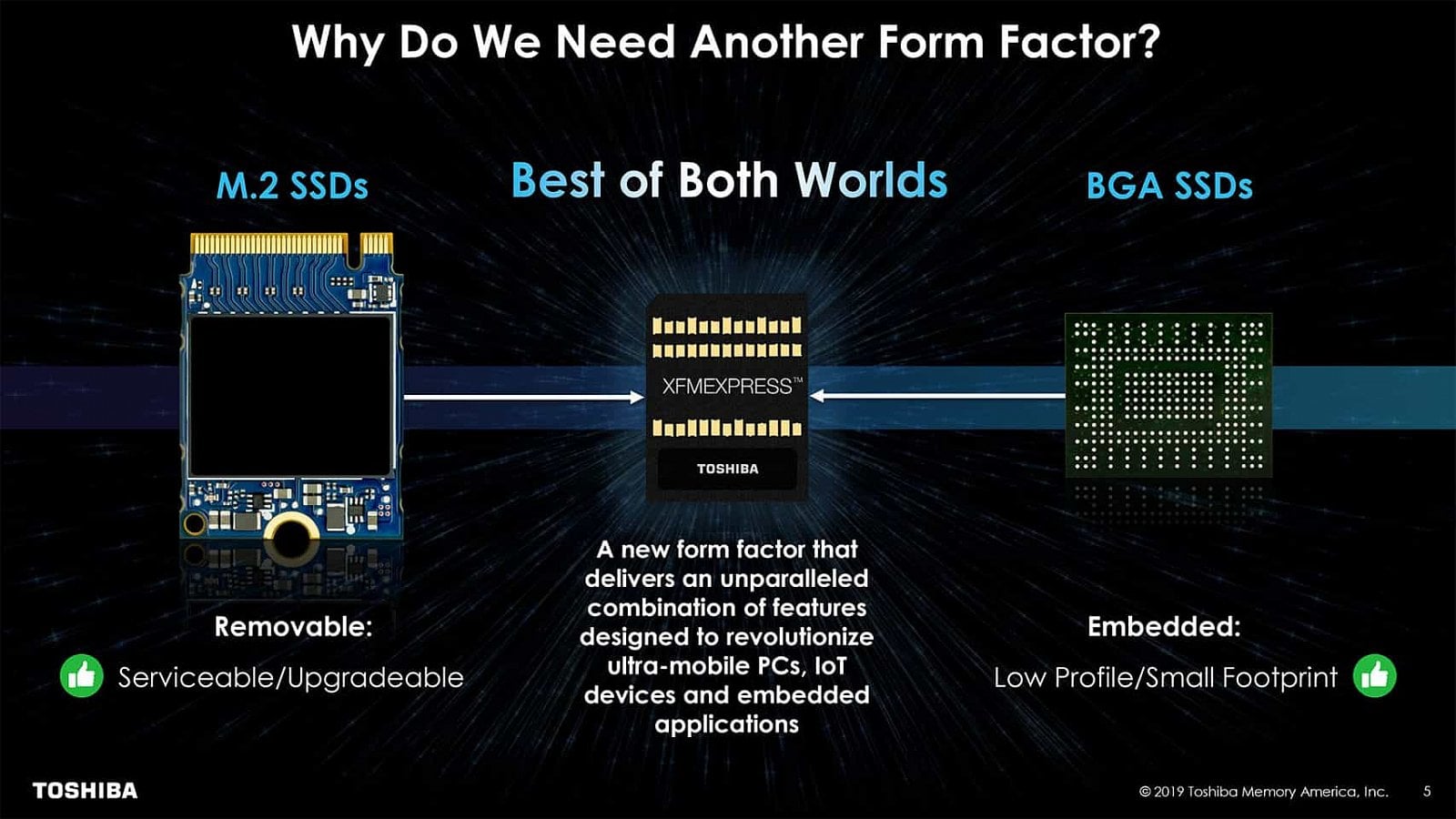

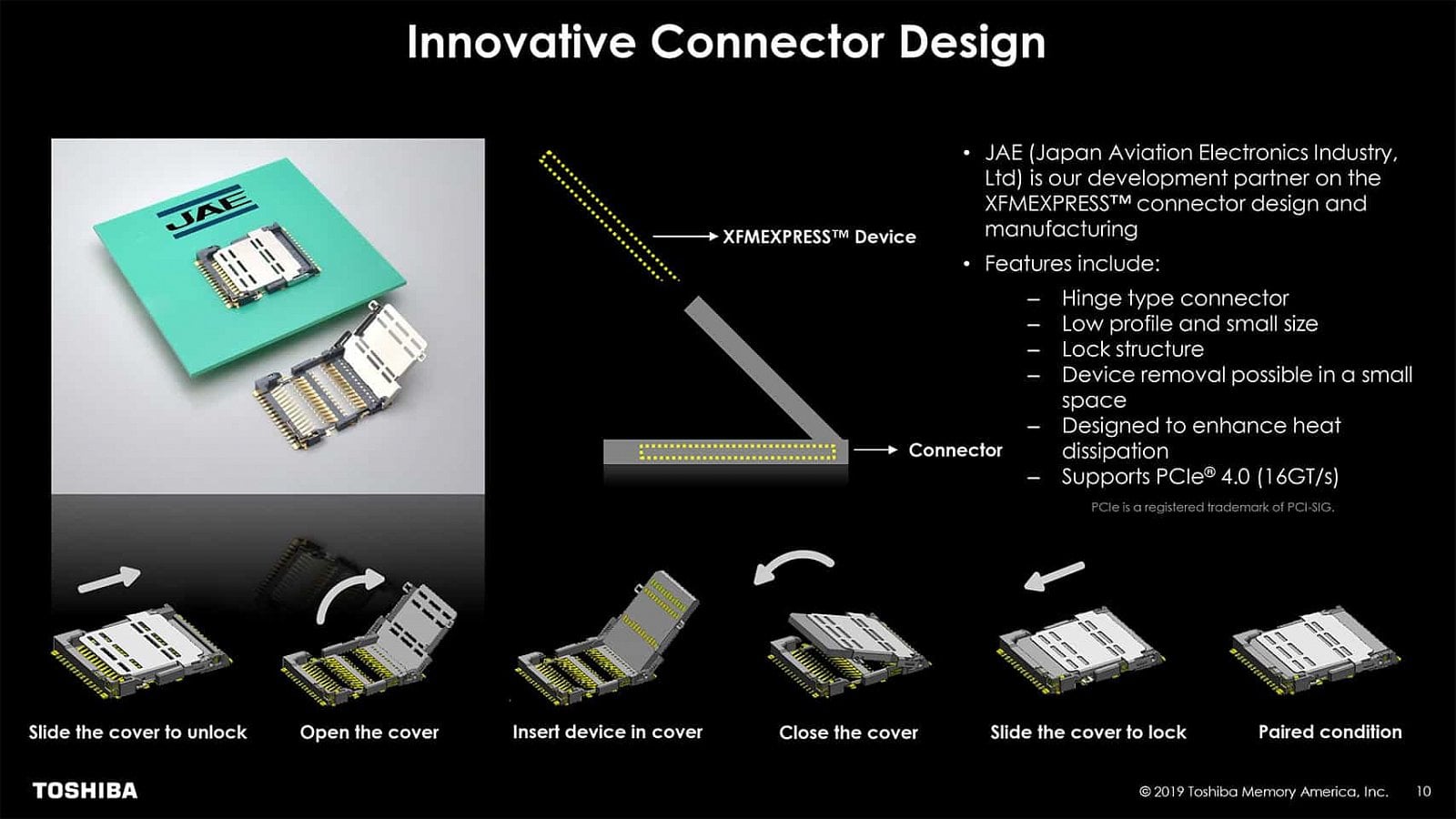

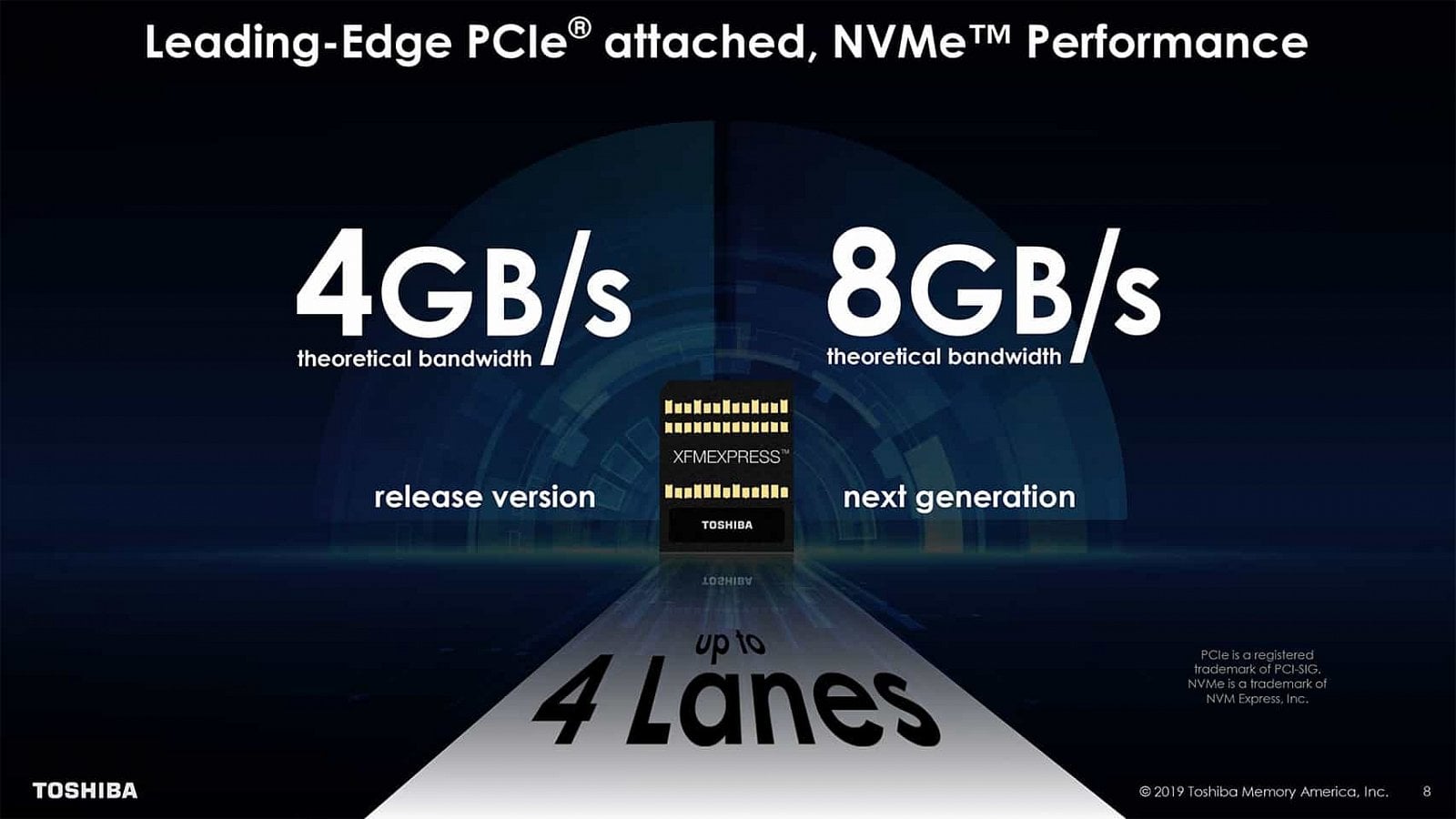

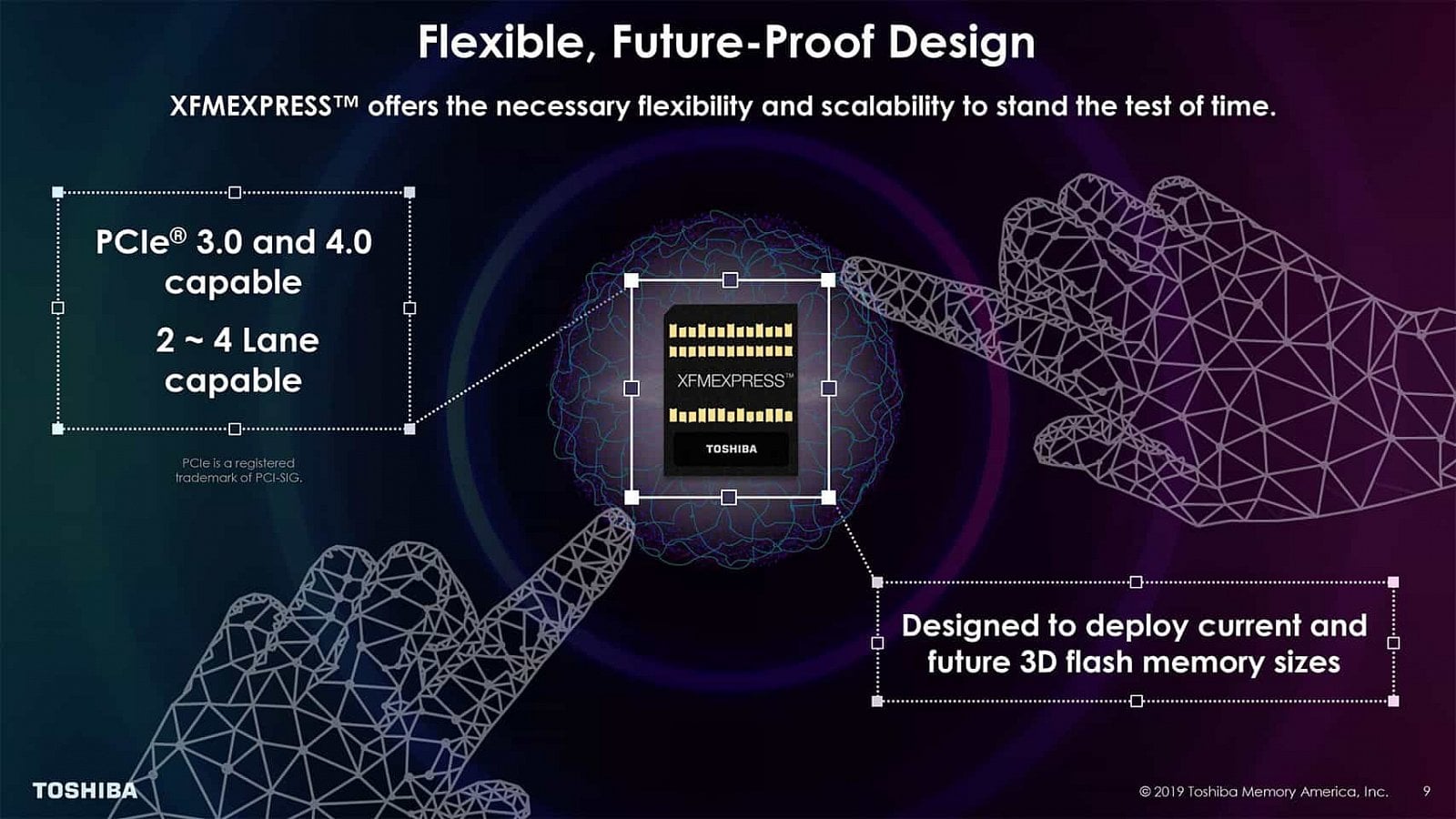

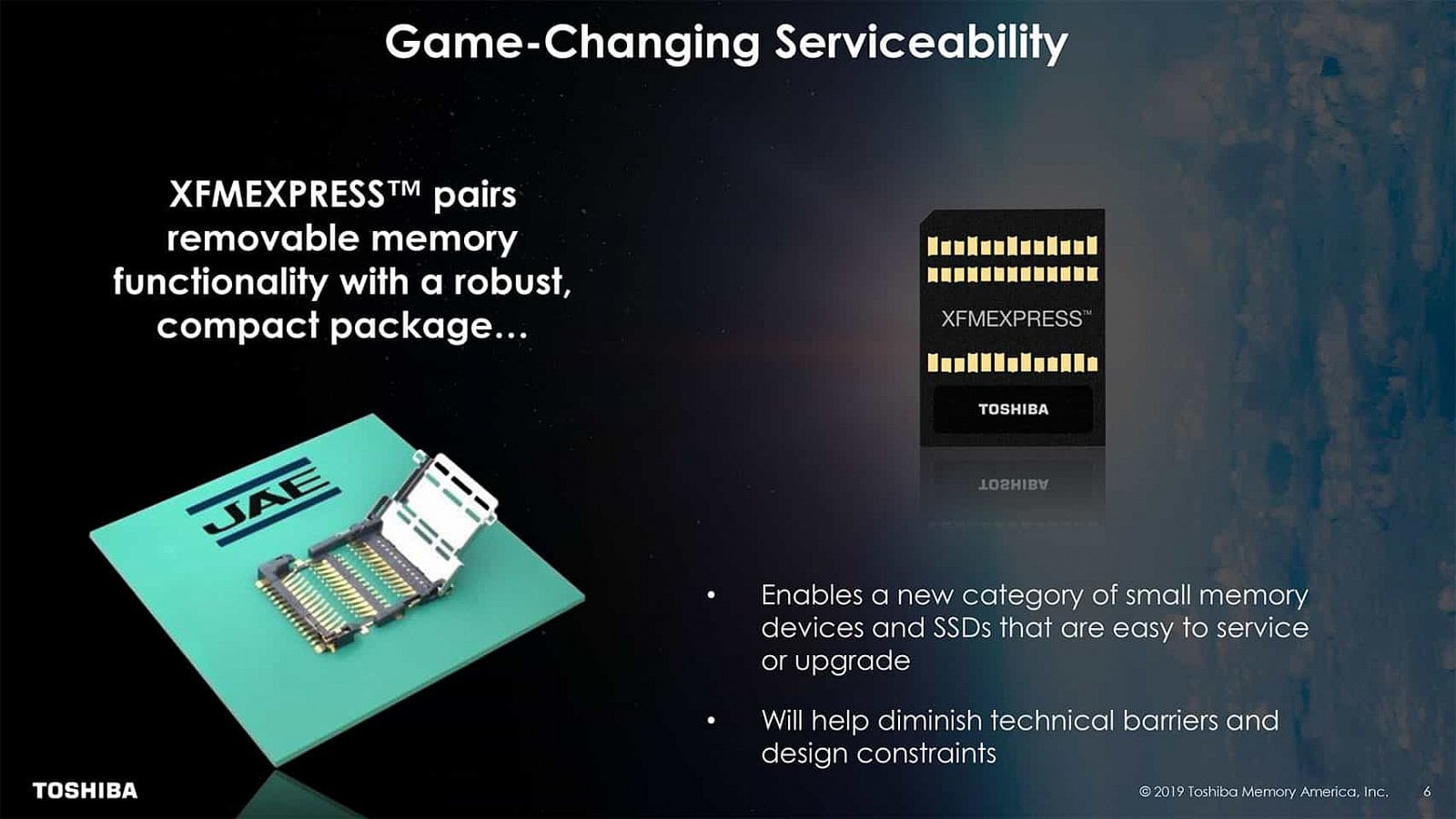

Tyto spády Toshiba – respektive zanedlouho Kioxia, protože flashová divize se přejmenovává – odhalila tento měsíc na Flash Memory Summitu, kde prezentovala mimo jiného (například nového rozhraní XFMExpress pro vyměnitelná kompaktní mobilní SSD) svou roadmapu pamětí NAND Flash, jejichž 3D NAND verzi firma oficiálně označuje jako „BiCS“. V některé z budoucích generací se pravděpodobně objeví PLC verze a Toshiba už zřejmě na jejím vývoji chvíli pracuje. Nyní totiž oznámila, že takovou vrstvenou NAND se záznamem PLC vyrobila o ověřila, že funguje. Mluvíme zde o Toshibě/Kioxii, ale ta pracuje společně se SanDiskem/WD, takže u nich by se tato technologie pak měla objevit také.

Tip: Naděje na opravitelné tablety a ultrabooky. Toshiba má malé vyměnitelné SSD

PLC má v tomto podání skutečně 5 bitů v jedné buňce, takže bude mít vyšší kapacitu na teoreticky stejně velký a stejně drahý čip. Ovšem už jen o 25 %, zatímco přechod z TLC na QLC zvedl ložnou plochu o 33 %. Přidávání dalších bitů po jednom má logicky klesající užitek. Spolehlivost a životnost přitom neškálují lineárně s nárůstem kapacity. Další bit totiž potřebuje dvojnásobek úrovní napětí (25 místo 24). To znamená, že buňka PLC musí ke svému fungování rozlišit 32 úrovní napětí a dlouhodobě je udržet, proti 16 úrovním u QLC a osmi u TLC. Bude tedy opět více náchylná na degradaci signálu v průběhu času, a opotřebení vlivem přepisů ji asi učiní nepoužitelnou mnohem dříve než v případě QLC.

5bitový záznam bude vyžadovat rozlišení 32 úrovní napětí v buňce. Prezentace PLC NAND od Toshiby na Flash Memory Summitu 2019. (Zdroj: Tom's Hardware)

5bitový záznam bude vyžadovat rozlišení 32 úrovní napětí v buňce. Prezentace PLC NAND od Toshiby na Flash Memory Summitu 2019. (Zdroj: Tom's Hardware)Zatím zde není řeč o nasazení záznamu PLC do praxe, takže těžko říct, kdy by se taková SSD mohla objevit. Na druhou stranu o QLC se také z počátku mluvilo jen opatrně jako o řešení pro „archivační“ disky, které by třeba zvládaly jen málo přepisů, a teď už je v běžných spotřebitelských SSD pro PC. I u PLC se nakonec přes všechna zhoršení vlastností může ukázat, že je schůdná.

Poznatky by mohly zlepšit i QLC a TLC

Podobně jako u QLC si spolehlivé čtení signálu z 32úrovňové buňky vyžádá zlepšení na stranách řadičů (přesnější čtení napětí, lepší ECC algoritmy), ale i čipů, aby byla podpořena zhoršující se robustnost. V tomto by zdá se mohl mít výzkum záznamu PLC i obecné přínosy, protože Toshiba uvádí, že některé z touto cestou nalezených zlepšováků by mohly být aplikovány i na QLC a TLC NAND. U těch by totiž také zlepšily vlastnosti a spolehlivost, ale mimo jiné i výkon.

Roadmapa 3D NAND firmy Toshiba/Kioxia

V současné roadmapě zatím není příchod čipů PLC oficiálně nikde stanoven. V současnosti je na trhu BiCS 4 s 96 vrstvami, Toshiba teď oznámila plány na BiCS 5, 6 a 7. Tyto nové generace by měly být částečně mířené na příchody nových verzí standardu PCI Express, které zvednou propustnost rozhraní pro úložiště, a tak mají mít i tyto čipy vyšší propustnosti, aby se výkon SSD v sekvenční rychlosti mohl také zvýšit.

BiCS 5 by měla brzy přijít na trh v SSD určených pro PCI Express 4.0, který už poskytují 7nm Ryzeny 3000 a serverové Epycy 7002 od AMD (a ještě déle také Power9 od IBM). Rychlost rozhraní čipů má stoupnout z 800 (BiCS 4) na 1200 MT/s, samozřejmě nevíme jistě, zda stejně stoupne i reálná sekvenční rychlost. Podle o něco starších informací by BiCS 5 měla přejít ze členění čipu na dva samostatné oddíly na čtyři oddíly, což má výkon výrazně zlepšit i v reálném používání. Čipy by prý měly být formované ze 128 vrstev.

Tip: 128vrstvá NAND od Toshiby a WD má o dost zlepšit výkon, přinese „4D“ design

BiCS 6 má poté přijít v éře rozhraní PCI Express 5.0 a používat rozhraní s o třetinu větší propustností (1600 MT/s). BiCS 7 bude pak určená po nadcházející PCI Express 6.0 a má používat rozhraní na efektivní rychlosti vyšší než 2000 MT/s, přesně to ještě uvedeno není. U těchto generací ještě informaci o počtu vrstev nemáme. Pro srovnání, nedávno oznámená nová generace vrstvené NAND od Samsungu má 136 vrstev a čeká se, že počty ještě v budoucnosti hodně porostou, Hynix například očekává až 500 vrstev.