Jaguar je následníkem jádra Bobcat, určeného pro levná, ale hlavně úsporná APU (AMD uvažuje o rozmezí TDP mezi 5 až 25 W). Jeho určením tedy budou tablety či různé hybridy, notebooky a levné desktopy. Firma ale naznačuje, že by uplatnění těchto jader mohlo být širší, zřejmě v čipech pro trh embedded a podobně.

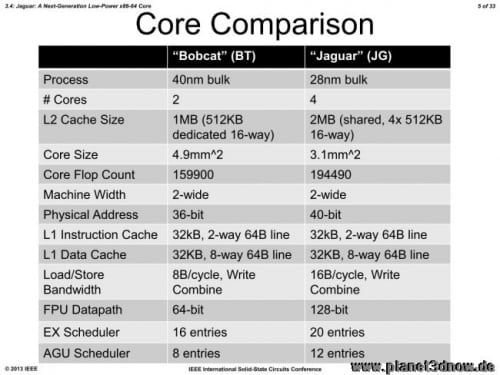

Jaguar má mít celkově IPC (tedy výkon za jeden takt) o víc než 15 % lepší než Bobcat, zatím však zřejmě jde o výsledky simulací. Celočíselné dělení by mělo být značně rychlejší, neboť procesor pro ně nyní bude mít hardwarovou jednotku. Již z dřívějška víme, že byla zdvojnásobena šířka jednotek SIMD (konečně jsou 128bitové). Podobně byla zdvojnásobena kapacita jednotek Load/Store, nyní zvládají 16 B za jeden takt místo 8. Zvětšeny byly i některé buffery pro vykonávání instrukcí out-of-order. Celkově je ale procesor stále stavěn na zpracovávání dvou instrukcí za takt.

Další drobná plus by mělo k výkonu přidat vylepšení přednačítání dat do instrukční cache. Zrychleno bude také uspávání a probouzení z úsporných stavů, což je důležité pro mobilní zařízení a notebooky. Většinu částí je možné odpojit od napájení, jádra a L2 cache lze odděleně odpojit od taktu. Slajdy zmiňují běh L2 cache na poloviční frekvenci oproti jádrům, není však jasné, zda jde o úsporný režim, či zda je cache níže taktována stále. Jaguar má být obecně schopen běžet na stejných taktech jako Bobcat při nižších napětích, do velké míry však asi půjde o důsledek přechodu na modernější výrobní proces.

Máme zde také oficiálně potvrzeno, že Jaguar bude podporovat nejnovější instrukční rozšíření. Zejména se jedná o akceleraci šifrování AES a 256bitové vektorové instrukce AVX. Ze starších byly doplněny SSE4.1 a SSE4.2. Dále bude mít čip také rozšíření CLMUL (carry-less multiplication), MOVBE (pro konverzi mezi formátem big-endian a little-endian), F16C (práce s čísly v plovoucí řádové čárce s poloviční přesností) a BMI1. Mimo zůstala podpora pro FMA a XOP, zřejmě by totiž čip velmi zkomplikovaly a zvětšily.

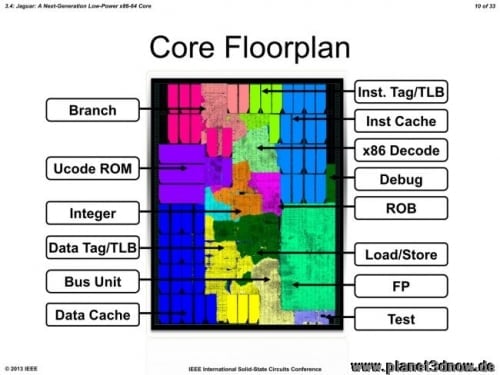

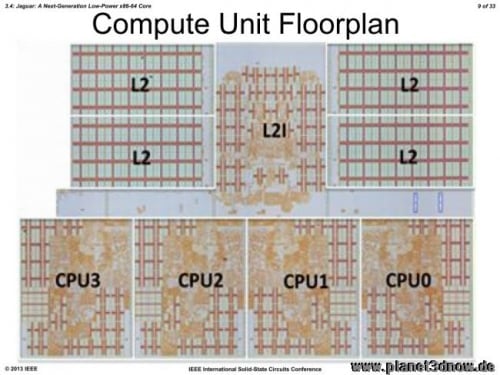

Na rozdíl od Bobcatu je Jaguar navržen jako celistvá čtyřjádrová jednotka s přiléhající sdílenou L2 cache o velikosti 2 MB – uspořádání můžete vidět na slajdu. Definitivně se potvrzuje, že čipy budou vyráběné 28nm linkami TSMC a půjde o proces typu HKMG. Návrháři se údajně soustředili na co největší hustotu tranzistorů: rozměr jednoho jádra klesl na 3,1 mm², zatímco jedno jádro Bobcatu měří na 40nm 4,9 mm². Na základě simulací by dosahované frekvence měly jít přes 1,85 GHz, což však není tak mnoho, uvážíme-li, že 22nm Atomy s out-of-order architekturou mají zvládat takty nad 2,5 GHz.

Procesorová „sekce“ architektury Jaguar je dle AMD určena k integrování do různých čipů typu SoC (zde se nabízí stará otázka, proč se vůbec AMD hodlá pro mikroservery trápit s jádry ARM Cortex). Firma uvádí, že při navrhování se hledělo i na to, aby se čip dal snáze přenést na jiný výrobní proces. Něco podobného však firma tvrdila již o Bobcatu, a jak víme, portace na 28nm proces u GlobalFoundries selhala (a k přenosu do TSMC nikdy nedošlo). Je docela možné, že praktické či časové důvody opět zamezí přechodu například na 20nm linku TSMC.

Zdroje: techPowerUp, Planet 3DNow!