Během posledních měsíců se řešilo, že procesory Intel Alder Lake odeberou podporu instrukcí AVX-512 v desktopech a noteboocích (poháněných Intelem) jen měsíce poté, co tyto instrukce přišly do desktopu. A aby se před pár týdny AVX-512 vrátilo se Zenem 4 paradoxně u AMD. Asi nejsme sami, kdo doufá, že krok Intelu je jenom dočasný a v budoucnu se u něj tato technologie zase vrátí. Bohužel to vypadá, že pokud tomu tak bude, pak to není nijak blízko.

Ačkoliv procesory Intel Raptor Lake vyjdou až za pár dní, už teď je jasné, že u nich se návrat AVX-512 konat nebude. Mají totiž pořád stejná malá jádra (E-Core) s architekturou Gracemont, která AVX-512 nepodporuje a která je vůbec tím důvodem způsobivším, že musely být tyto instrukce přes funkční implementaci v křemíku vypnuté i u velkých jader (nejdřív reverzibilně, později natvrdo). Raptor Lake lze téměř označit za refresh či rozšíření generace Alder Lake.

Tudíž první možnost pro návrat AVX-512 byly až procesory následující generace s kódovým označením Meteor Lake. Ty by mohly vyjít někdy v druhé polovině roku 2023 jako Intel Core 14. generace a podle předběžných informací mají opět upravená nebo nová velká jádra P-Core (Redwood Cove), ale také novou architekturu jader E-Core označenou Crestmont (také už ale mimochodem budou na nové platformě – v desktopu pro ně přijde nový socket LGA 1851).

Protože je architektura E-Core nová, byla šance, že v ní Intel již implementuje AVX-512 (klidně třeba s použitím 256bitových jednotek SIMD, jako to dělá AMD Zen 4), takže by již hybridní architektura big.LITTLE nevytvářela nekompatibilitu a AVX-512 mohlo být zase zapnuté i na velkých jádrech Redwood Cove.

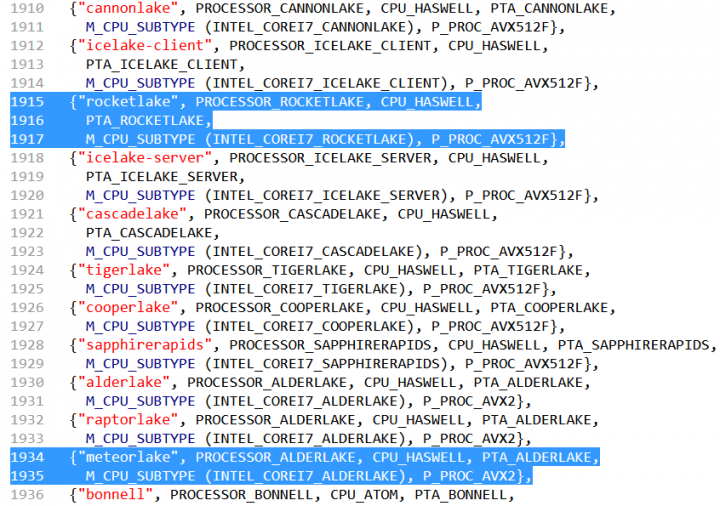

Tyto naděje teď bohužel můžeme odškrtnout. Intel začal zasílat patche s podporou CPU architektur použitých v procesorech Meteor Lake do různých open-source programů, mezi nimiž je i překladač kódu GCC. V patchích pro kompilátor jsou jasně uvedené všechny instrukční sady, které procesor podporuje (protože překladač má mít schopnost emitovat různé instrukce podle toho, jaký procesor je cílem), a pro Meteor Lake mezi nimi AVX-512 bohužel opět není.

Kód zaslaný do GCC prozrazuje, že Meteor Lake bude opět poskytovat jen AVX2 (zdroj: GNU, Git repozitář GCC)

Kód zaslaný do GCC prozrazuje, že Meteor Lake bude opět poskytovat jen AVX2 (zdroj: GNU, Git repozitář GCC)Jádra Crestmont tedy stále budou podporovat jen instrukce třídy AVX a AVX2 s 256bitovými registry YMM (AVX-512 běží nad 512bitovými registry ZMM), Intel se v této generaci ještě nedostal k tomu, aby u nich SIMD povýšil. A stejně jako u Alder Lake a Raptor Lake to tedy také znamená nemožnost používat AVX-512 na velkých jádrech.

- Tip: Test Rocket Lake a AVX-512: jak ho zapnout v x265 a jaký je výkon a spotřeba?

- Tip: AVX-512 na Ryzenech 7000: jak užitečné je a je implementace od AMD lepší než Intelu?

AVX-512 až v Lunar Lake?

Zde je možná dobré říct, že roadmapa malých jader Intelu byla alespoň v uplynulých letech koncipována s pomalejším střídáním architektur než roadmapa velkých jader P-Core. Vidíme to nyní, kdy architektura E-Core Gracemont poslouží ve dvou generacích procesorů (Alder Lake, Raptor Lake).

Roadmapa procesorových architektur Intel, prosinec 2018. Můžete vidět, že tzv. malá jádra, z nichž se vyvinula E-Core, mají či tehdy měla poloviční kadenci vývoje (zdroj: AnandTech)

Roadmapa procesorových architektur Intel, prosinec 2018. Můžete vidět, že tzv. malá jádra, z nichž se vyvinula E-Core, mají či tehdy měla poloviční kadenci vývoje (zdroj: AnandTech)Tedy je docela pravděpodobná možnost, že také architektura Crestmont bude také využitá ve dvou generacích, což by způsobilo, že po Meteor Lake bude AVX-512 prakticky nemožné i v následující 15. generaci Core (2nm či 3nm Arrow Lake v roce 2024).

Další šance pro opětovné nasazení AVX-512 do „klientských“ (pro desktop a notebooky) procesorů Intel by tak byla až v roce 2025 s 1,8nm procesory Lunar Lake (Core 16. generace, pokud se do té doby značení nezmění).

Více: Jaké chystá Intel procesory? Arrow Lake a Lunar Lake potvrzené na 2024–2025, 20A a 18A proces

Do té doby (nebo v lepším případě do roku 2024 s Core 15. generace) tedy asi uživatelé nebo programátoři budou moci získat přístup k instrukcím AVX-512 jen v procesorech AMD s architekturou Zen 4 či Zen 5, nebo koupí-li si nějaký highendový nebo serverový Xeon od Intelu, ať už nový, nebo bazarový.

Zdroje: Phoronix, GNU / Git repozitář GCC