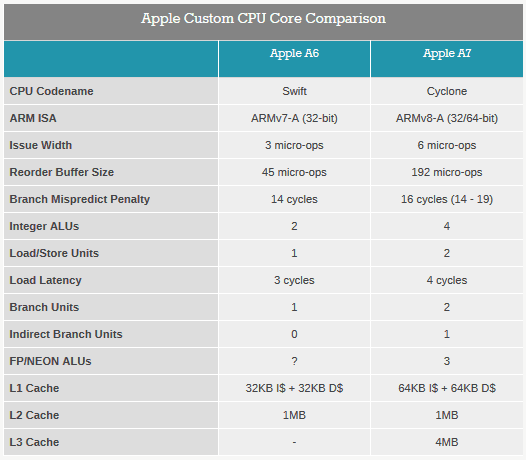

Podle zjištění webu AnandTech, který zkombinoval údaje odhalené v kódu kompilátoru LLVM s výsledky valstních benchmarků, byla architektura Swift použitá v předchozí generaci čipů Apple (A6) ještě poměrně standardním „malým jádrem“ snad srovnatelným s Cortexem-A15: Swift byl stavěn na zpracování/dekódování třech instrukcí najednou (tzv. „3-issue“), obsahoval dvě ALU a jednu jednotku pro načítání/ukládání do paměti (load/store unit). U architektury Cyclone použité v čipu A7 se ale Apple nespokojilo s přidáním 64bitového režimu. Ve skutečnosti navrhlo dramaticky výkonnější jádro, snad dokonce přímo srovnatelné s velkými architekturami Intelu jako je Sandy Bridge či Haswell.

Architektura Cyclone měla loni premiéru v čipu Apple A7

Cyclone má dvojnásobnou šířku – v jednom cyklu upracovává šest instrukcí („6-issue“). Jádro disponuje již rovnou čtyřmi ALU (aritmeticko-logickými jednotkami; tolik dostal od Intelu až Haswell). Zdvojnásoben je i počet jednotek pro čtení/zápis paměti a jádro má i dvě jednotky pro větvení (Swift měl jednu). FPU má tři výpočetní jednotky s podporou SIMD rozšíření Neon. Zdvojení výpočetních prostředků odpovídá zdvojnásobení L1 cache – má teď 128 KB (64 KB data, 64 KB instrukce) jako svého času architektury K7 až K10 od AMD, Haswell má celkem jen 64 KB. L2 cache zůstává u Cyclone na velikosti 1 MB, ale čip má navíc L3 cache o kapacitě 4 MB.

Že je třeba Cyclone chápat jako „velké jádro“ nasvědčuje také velikost reorder bufferu, do nějž se vejde 192 instrukcí (respektive μopů). Systém out-of-order vykonávání instrukcí je tedy dosti vyvinutý – stejně velké „pracovní okno“ má pro pořádání instrukcí i Haswell (pro srovnání: u Swiftu měl reorder buffer kapacitu jen 45 μopů). Zde je ale třeba dodat, že mezi architekturou x86 a ARMv64 jsou poměrně zásadní rozdíly a čísla tedy nelze srovnávat úplně slepě. Kód x86 obvykle udělá „více práce“ v přepočtu na instrukci (jelikož instrukce jsou komplexnější a zahrnují i práci s pamětí) a na jeden bajt.

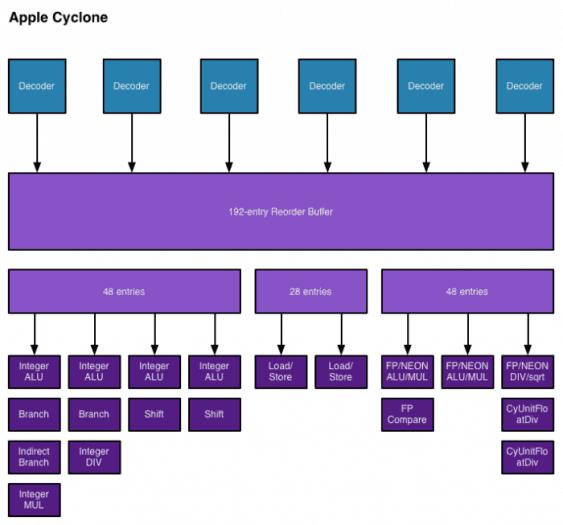

Cyclone, schéma jádra CPU (Zdroj: AnandTech)

Procesor má zřejmě oddělené schedulery pro ALU, FPU – tyto fronty pojmou 48 instrukcí – a pro jednotky load/store (24 instrukcí). Celočíselná část umí provést v naráz čtyři sčítání, FPU dokáže zpracovat tři vektorová sčítání naráz nebo dvě násobení. Dělit umí jen jedna z jednotek, což je ale obvyklé. Jak ALU, tak FPU zřejmě lze vytížit naráz – A7 umí v jednom taktu provést čtyři celočíselné součty a dva součty instrukcemi Neon.

Srovnání Cyclonu s předchozí architekturou Swift, jak jej vypracoval server AnandTech

Apple od Swiftu také prohloubil pipeline procesoru – nasvědčuje tomu alespoň výkonnostní postih za chybně odhadnuté větvení, který činí čtrnáct až devatenáct cyklů (u Swiftu to bylo 14). To naznačuje, že pipeline by mohla být obdobně dlouhá jako u Haswellu či Sandy Bridge, které vykazují u špatného větvení podobné postihy. Latence načítání dat (z L1 cache) narostla z tří cyklů na čtyři. Je možné, že výsledkem těchto úprav bude zvýšení frekvenčního stropu pro celé jádro. V současnosti ale Apple dodává A7 jen na nízkých frekvencích (1,3–1,4 GHz), kde by snad nějaké preventivní prodlužování pipeline nemělo být nutné, takže počítám, že jde spíše o přípravu „do budoucna“.

Bude Apple novým vyzyvatelem Intelu?

Dle oficiálních údajů má dvoujádrový SoC A7 plochu 102 mm² a obsahuje přes miliardu tranzistorů. Jádra Cyclone jsou z hlediska architektury evidentně mnohem silnější než všechny dosavadní Cortexy (včetně 64bitového Cortexu-A57), Krait od Qualcommu, ale také Silvermont či Jaguar. Výkon na jeden takt (tzv. IPC) by měl být u architektury Applu mnohem vyšší, ale je pravda, že jednodušší jádra konkurence mohou tento náskok zmenšit, pokud poběží na vysokém taktu (což je dnes ve sféře čipů ARM cokoliv nad 2 GHz), nebo pokud nabídnou více jader.

Zda by Cyclone mohl skutečně být konkurencí pro Haswell a zda by jej Apple mohlo nasadit v noteboocích či desktopech (spekuluje se o tom již dlouho), to je zapeklitá otázka. Předně nevíme, jak moc dokáže Cyclone škálovat na vyšší frekvence a tedy výkony – jak už bylo řečeno, zatím se Apple zastavilo pod půldruhým gigahertzem. Spotřeba čipu by také řekněme na 3–4 GHz (pokud by na tyto takty vůbec dosáhl) mohla být již neúnosná. Možné je také, že by se na srovnatelných taktech projevila různá úzká místa ve výkonu, která u mobilního čipu ještě nejsou podstatná.

S těmito výhradami je ale třeba říci, že Apple zřejmě má minimálně potenciál na to, aby velký desktopový procesor vyrobilo. Mezi čipy ARM má nyní dle všeho nejprogresivnější architekturu (něco podobně ambiciózního ale údajně chystá Nvidia, jejíž Denver možná bude dokonce 7-issue, tedy ještě „širší“). Je docela škoda, že se procesory Apple nedostanou do zařízení jiných výrobců a platforem – mimo jiné to totiž stěžuje porovnání s konkurenčními architekturami. Pokud by se Apple eventuálně stalo hlavním technologickým soupeřem Intelu v oblasti CPU (ruku na srdce, tuto roli nyní AMD docela silně nestíhá), vznikla by absurdní situace, kdy byste čipy procesorové dvojky(či nedejbože dokonce jedničky mohli používat jen v počítačích Mac, iPadech a iPhonech.

Zdroj: AnandTech