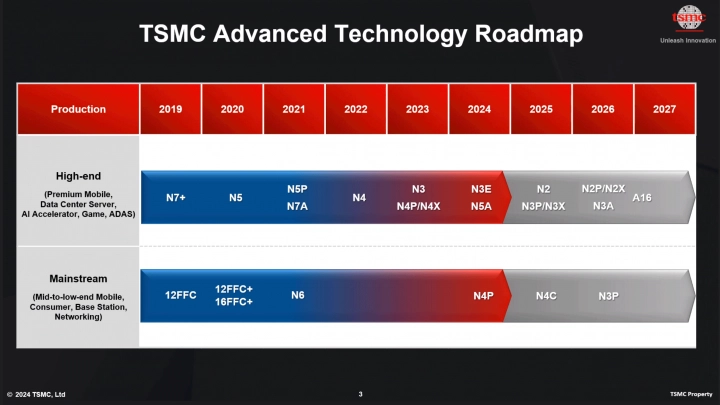

Intel letos oznámil svůj next-gen výrobní proces 14A (1,4nm technologii), který bude první následující po už delší dobu slibované (a provázané) sérii technologií Intel 4 a 3 a Intel 20A a 18A. Konkurenční TSMC, které je etalonem, který se Intel snaží dohonit, teď také prozradilo své plány ohledně budoucnosti následující po 2nm procesu. Tím dalším stupněm pro něj bude 1,6nm proces který také přejde na angströmové značení a bude se jmenovat A16.

TSMC A16

Proces A16 teď TSMC oznámilo na své konferenci v Santa Claře. Tento proces bude používat tranzistory na bázi tzv. nanodestiček (nanosheet), půjde tedy o tranzistory typu GAAFET. Tento prvek by měl ale být aplikovaný už v předchozí generaci 2nm procesu, na 1,6nm (16angströmové) technologii už tedy půjde o druhou generaci GAAFETů. Intel tyto tranzistory nasazuje na procesu 20A a Samsung na 3nm technologii.

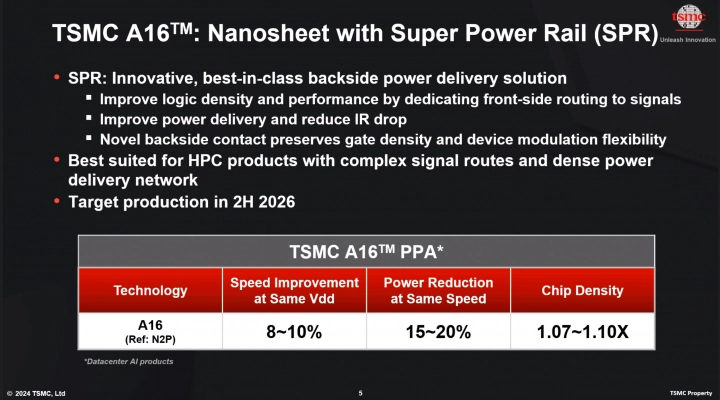

Proces A16 má podle TSMC přinést o 8–10 % lepší výkon (tedy vyšší frekvenci) při určité úrovni napětí a komplexitě obvodu ve srovnání s 2nm procesem N2P. Alternativně, pokud výrobce čipů nezmění frekvenci směrem nahoru, by technologie mohla snížit spotřebu určitého návrhu čipu o 15–20 %. Co zatím není zmíněno, jsou nějaké přesné údajně o hustotě tranzistorů, ale hustota čipů by prý mohla být zlepšená o 7–10 %.

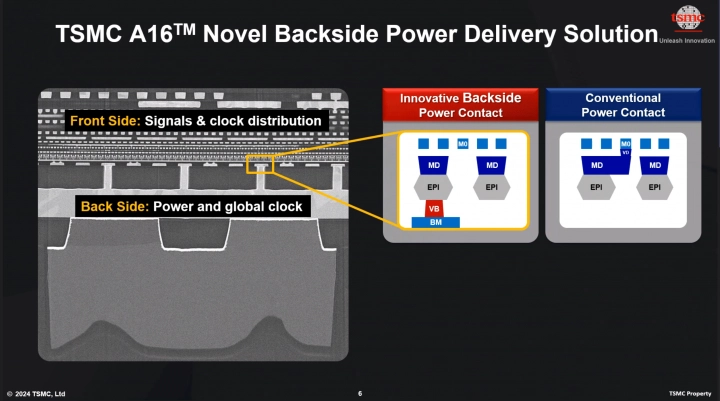

Zatímco GAAFETy nebudou v procesu A16 nové, v tomto procesu TSMC bude jako v prvním této firmy použitá technologie Backside Power Delivery (či také Backside Power Delivery Network). To je radikální nová věc v návrhu, ale i výrobě čipů, jde asi o největší převrat v systému výroby čipů a větší změna než použití 3D tranzistorů (FinFETů).

Co je Backside Power Delivery?

Konvenčně jsou čipy vyráběné tak, že na povrchu křemíkové desky jsou tvořené polovodičové struktury (do křemíku) a na ně se pak nanášejí kovové vrstvy vodičů (tzv. BEOL), kterých je několik (i 10–20). Začíná se přitom nejjemnějšími vodiči, které slouží k propojení tranzistorů přímo v nejjemnějších strukturách integrovaného obvodu a potřebují největší přesnost včetně nutnosti použití EUV expozice. Na ně se pak nanášejí hrubější vrstvy a ty nejhrubší jsou pak na vrchu zpracovaného čipu, kde už jsou vytvořené i kontaktní plošky pro napájení čipu na substrát. Tyto hrubší kovové vrstvy slouží hlavně k napájení.

Nicméně jak se čipy miniaturizují, kovové vrstvy se stávají čím dál větším limitem (způsobovaly prý největší problémy v 10nm procesu Intelu) a i samotné napájení začíná být těžkým problémem. K tranzistorům na spodku tohoto souvrství je totiž nutné přivádět čím dá více proudu, ale je k tomu čím dál méně místa, protože i logické propojení tranzistorů potřebuje svoji plochu ve hlubších jemných kovových vrstvách. Napájení jednoduše řečeno koliduje se zhušťováním logických obvodů a jeden aspekt omezuje ten druhý.

Backside Power Delivery přichází proto s radikálním řešením – odebrat napájecí vodiče ze stávajících vrstev kovových spojů, které se při výrobě vytvářejí na povrchu křemíku. Backside Power Delivery místo toho zavádí separátní souvrství kovových vodičů na druhé straně křemíku, které je vyhrazeno jen pro napájení. To je tak možné posílit a současně je možné zlepšit hustotu logických obvodů.

Nevýhodou je ale o hodně komplikovanější výroba, kdy musíte už zpracovaný wafer otočit, obrousit ho na menší tloušťku a tam pak aplikovat nové kovové vrstvy, které se k tranzistorům budou muset „dostat“ pomocí TSV vyhloubených do křemíku. Toto bude pravděpodobně jedna z největších výzev při vývoji souvisejících procesů a hodně se tím vše zkomplikuje – proto je také tato technologie nasazována až nyní.

Super Power Rail – přístup TSMC bude nejpokročilejší, ale i nejdražší

Backside Power Delivery může být realizována různými způsoby. Imec vyvinul metodu Buried Power Rail, která má rozvod napájení k jednotlivým tranzistorům pořád vyvedený v rámci hlubších konvenčních kovových vrstev, které už existují dnes, ale samotná distribuce napájení do těchto vrstev je dělaná novými vrstvami na zadní straně křemíku, které jsou na (konvenční) kovovou vrstvu na přední straně čipu napojené pomocí TSV v různých místech.

Intel má technologii nazvanou PowerVia (poprvé v procesu 20A), která by měla mít granularitu napojení nových zadních vrstev vodičů mnohem jemnější, na úrovni logických bloků, nebo dokonce i na kontakt tranzistorů. Toto je mnohem komplexnější na výrobu.

TSMC svou technologii označuje Super Power Rail a měla by přivádět napájení ze zadních napájecích kovových vrstev přímo na source i drain elektrody každého tranzistoru. Podle TSMC by tato forma Backside Power Delivery měla být nejefektivnější pro zlepšení hustoty čipů, ale je z implementací nejkomplexnější a také nejdražší na výrobu.

Dostupnost 2026–2027

Technologie by podle plánů TSMC měla být přichystaná v roce 2026, kdy má začít sériová výroba. Reálná komerční dostupnost čipů ale obvykle následuje s nějakým zpožděním, takže 1,6nm čipy TSMC asi nebudou na trhu před rokem 2027. Jako první nejspíš (to je však jen dohad) tento proces použije firma Apple, která má nejhlubší kapsy a bývá v použití nových procesů nejagresivnější.

Tento harmonogram samozřejmě nelze zaručit. TSMC má sice lepší historii plnění cílů a pravděpodobně i více zkušeností a schopností než Intel, ale komplexita těchto technologií pořád strmě roste, a tak se i u TSMC může vývoj opozdit. To už se ostatně fakticky stalo s 3nm technologií.

Zdroj: AnandTech