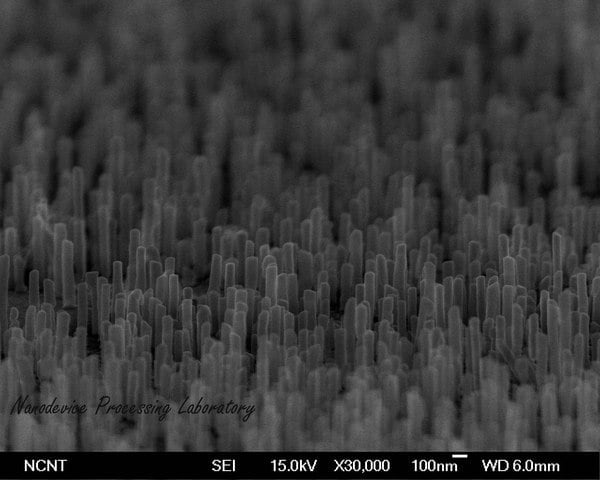

O tomto směru výzkumu jste možná již slyšeli. Princip je velice jednoduchý. Při klasickém výrobním postupu kanál tranzistoru probíhá vodorovně v rovině (nebo na ní v případě FinFETů tvoří cosi jako zídku). Hradlo tranzistoru (které je zodpovědné za „otevírání“ a „uzavírání“ kanálu) je pak položeno na kanálu nebo okolo něho (u FinFETu). Tranzistory založené na nanodrátcích naopak používají kanál ve formě jakého sloupečku, který svisle vyrůstá z roviny. Je tvořen právě nanodrátkem, tedy úzkou polovodičovou tyčinkou. Hradlo (či hradla) je pak vybudováno okolo sloupečku/nanodrátku a tvoří jakýsi obal. V ideálním případě by kanál obepínalo ze všech stran a po celé délce.

Jak vidíte, takovýto tranzistor je již plně trojrozměrnou strukturou. Pokud ho chcete vytvořit, musíte vlastně vést vodiče v několika rovinách (emitor a kolektor tranzistoru jsou přímo nad sebou). Výroba tak bude logicky mnohem náročnější, než u řešení jako jsou FinFETy. Na druhou stranu by měl takovýto svislý tranzistor mít lepší vlastnosti. Například by měl méně trpět úniky proudu.

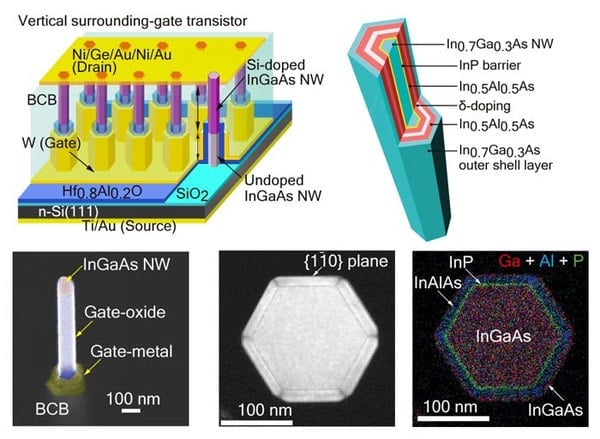

Právě s problémem, jak z nanodrátků úspěšně vztyčit kanály tranzistorů a opatřit je funkčními hradly, se popasovali vědci z univerzity v Sapporu na japonském ostrově Hokkaidó. Týmu vedenému profesorem Kacuhirem Tomiokou se jednak podařilo vyrobit kanály (tedy nanodrátky). Navíc ale japonští vědci demonstrovali i způsob, jak kolem sloupcovitého kanálu realizovat hradlo. To je tvořeno několika různými vrstvičkami (hradlo musí být mimo jiné izolováno od kanálu), které tvoří jakýsi plášť nanodrátku. Pochopitelně je spojené s kontaktem, z kterého lze na hradlo přivést proud pro přepnutí tranzistoru.

Vertikální tranzistorové struktury, které se podařilo vytvořit, mají šestiboký průřez. Tvořeny jsou z několika materiálů, použito bylo india, galia, arzenu, fosforu a hliníku. Vyrobené hexagonální vertikální tranzistory mají údajně velmi dobré vlastnosti. Proudy procházející ve vypnutém a zapnutém stavu se prý liší řádově až poměru 1 : 100 000 000. Vlastnosti těchto struktur by prý již nyní měly překonávat konvenční křemíkové tranzistory, a to při srovnatelném půdorysu. Vědci se nyní pokusí postup vypracovat do podoby, která by umožnila vytvořit tranzistory použitelné v logických obvodech.

Stejně jako mě vás asi zajímají dopady tohoto objevu z praktického hlediska. Jak už to však bývá, výhled na sériové nasazení vertikálních tranzistorů není nijak růžový. Zatím jsme se (pomineme-li Tri-Gate Intelu) ještě nesetkali ani s FinFETy, které mají ve výrobnách nastoupit na 20nm (UMC) až 14nm (TSMC) procesu v letech 2014 a 2015. Tranzistory z nanodrátků budou přitom asi značně tvrdším oříškem. Je možné, že se jich dočkáme až v další dekádě – pokud vůbec někdy.

Může se totiž stát, že v době, kdy budou použitelné v praxi, už to tradiční materiály budou mít za sebou a nahradí je třeba grafen. Přinejmenším výsledky stávajícího výzkumu přitom asi v grafenové litografii nemusí být mnoho platné. S tím, jak se budou měnit materiály používané k výrobě čipů, se nakonec může ukázat, že nanodrátky tím ideálním řešením nebudou.

Zdroj: nanotechweb.org