Ze starších zpráv o procesorech Intel Haswell jsme se dozvěděli mimo jiné to, že nabídka integrovaných grafických jader se rozroste na tři varianty a nejvýkonnější GT3 překoná IGP dnešního Sandy Bridge možná až pětinásobně. Zřejmě ale už i Intel narazil na problém s propustností paměti – o nijak závratně rychlé DDR3 na dvou kanálech se integrované grafické jádro musí dělit se čtyřmi výkonnými procesorovými jádry. AMD tento problém u svých APU řeší tak, že oficiálně podporuje rychlejší moduly s taktem 1866 MHz. Inženýři Intelu ale nejspíš dospěli k názoru, že ani to nestačí.

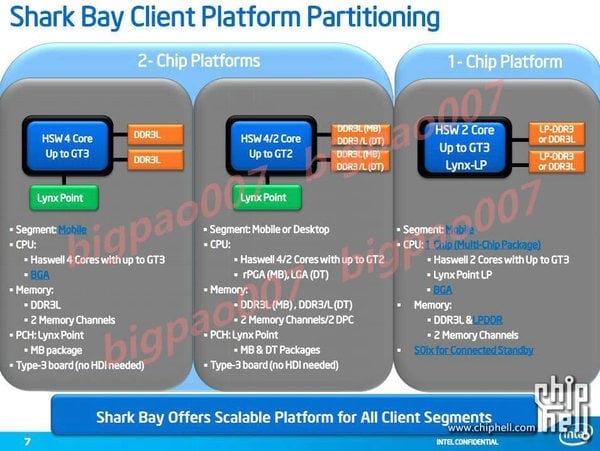

Připomeňme si starší slajd zobrazující možnosti platformy Shark Bay. Napovídá nám, že Haswell bude fyzicky existovat ve třech variantách. Zatímco v desktopu bude vrcholem nabídky čtyřjádro s grafikou třídy GT2, pro standardní notebooky bude k mání quad-core s GT3. A právě tyto čipy, nebo spíše vybrané modely na nich postavené, budou podle VR-Zone vybaveny ještě externí cache. Jelikož Haswell má dnes již klasicky tři úrovně cache, tato bude tudíž L4.

Nákres výše ukazuje, jak by to asi mohlo vypadat. Vzhledem k tomu, že patice budou stejné pro verze s L4 cache i bez ní, řešení ve stylu Pentia II (cache na základní desce připojená přes back-side bus) není pravděpodobné a tak bude příruční paměť nejspíše v jednom balení s procesorem.

Záhadou zatím je, k čemu bude tato cache používána. Možnosti jsou v zásadě tři. Cache může být buď sdílená mezi CPU a GPU (pro účely vyměňování dat má ale Haswell sdílenou L3 cache), nebo pouze pro procesor (ten tak bude méně často přistupovat do hlavní paměti), nebo pouze pro grafické jádro. Vedle notoricky známého příkladu GPU Xenos s eDRAM si můžete vzpomenout též na sideport paměť u integrovaného Radeonu HD 4200 v čipsetu AMD 785G; ačkoliv jeho primárním účelem bylo umožnit paměťovému řadiči v procesoru přejít do režimu spánku, měl i blahodárný účinek na grafický výkon.

L4 cache Haswellu ale s nejvyšší pravděpodobností nebude připojena přes standardní rozhraní DDR3, neboť to má pro dva čipy na jednom balení zbytečně vysokou latenci. Ostatně, k čemu by Intelu byly standardy pro takovéto unikátní řešení? Stačí, aby byl čtyřjádrový Haswell s GT3 odpovídajícím rozhraním, které menší čipy mít nemusí.

Zdroj: VR-Zone