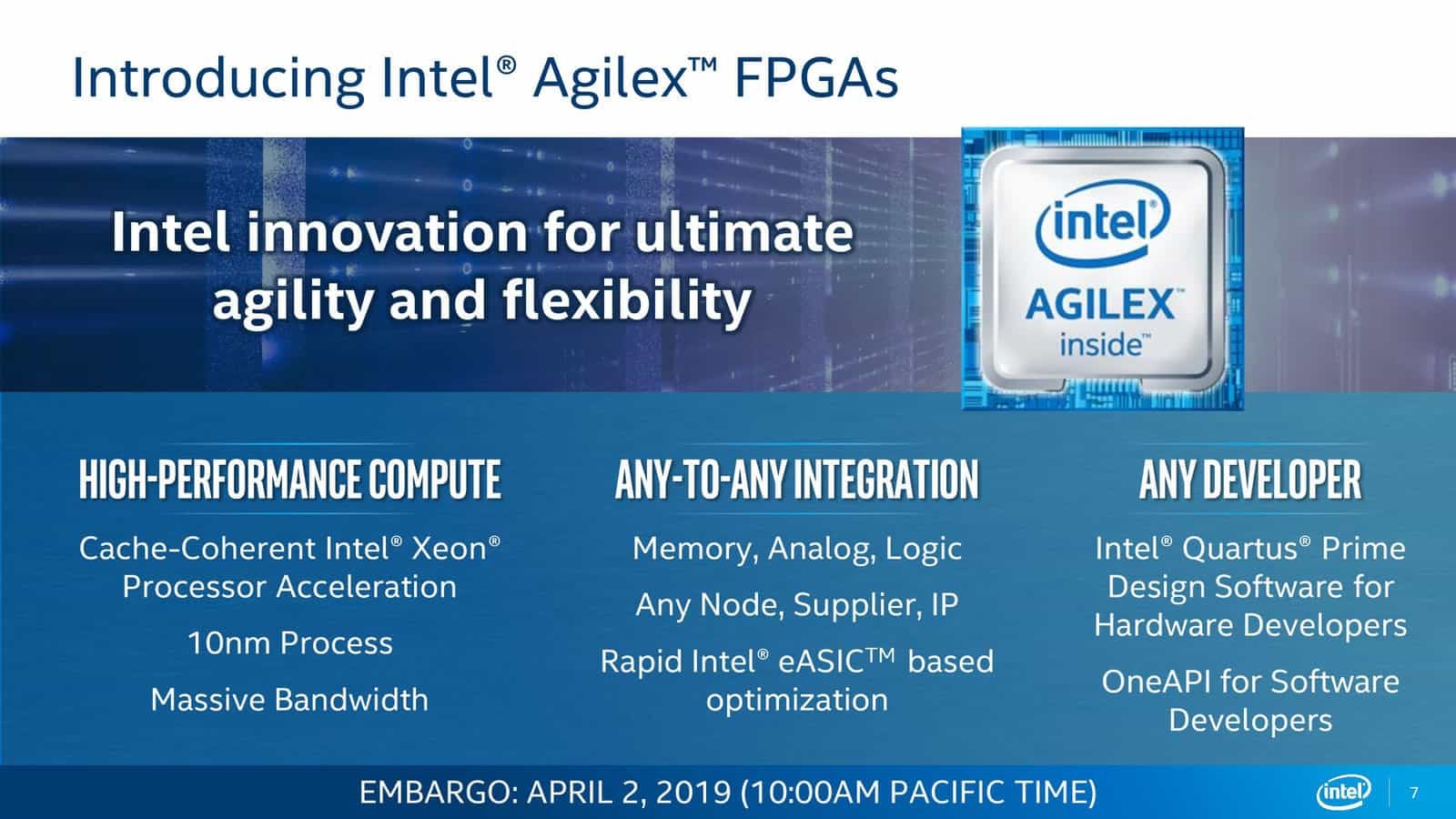

Tento týden Intel uspořádal velké společné odhalení mnoha různých produktů pro serverový (či datacentrový) trh. Ústřední roli v tom hráli nové Xeony Cascade Lake, v „Advanced“ verzi s až 56 jádry. Nebyla to ale jediná novinka. Intel také odhalil nová FPGA od své divize Altera. Čipy Agilex jsou vyráběné na jeho problémovém, ale pomalu přece jen přicházejícím 10nm procesu, ale není to rozhodně jediná věc, kterou jsou pozoruhodná.

10nm, čiplety, DDR5, PCI Express 5.0, CXL

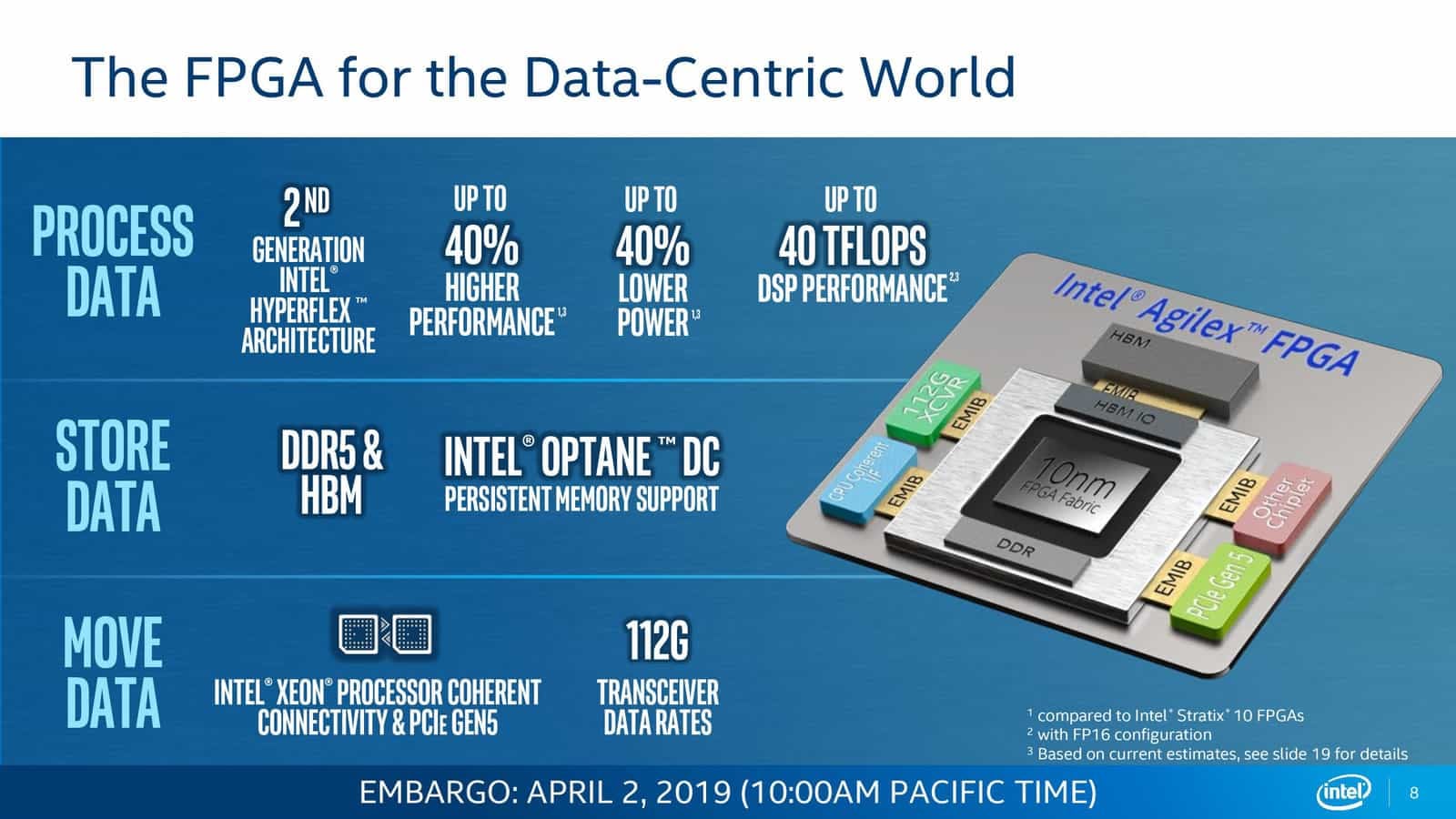

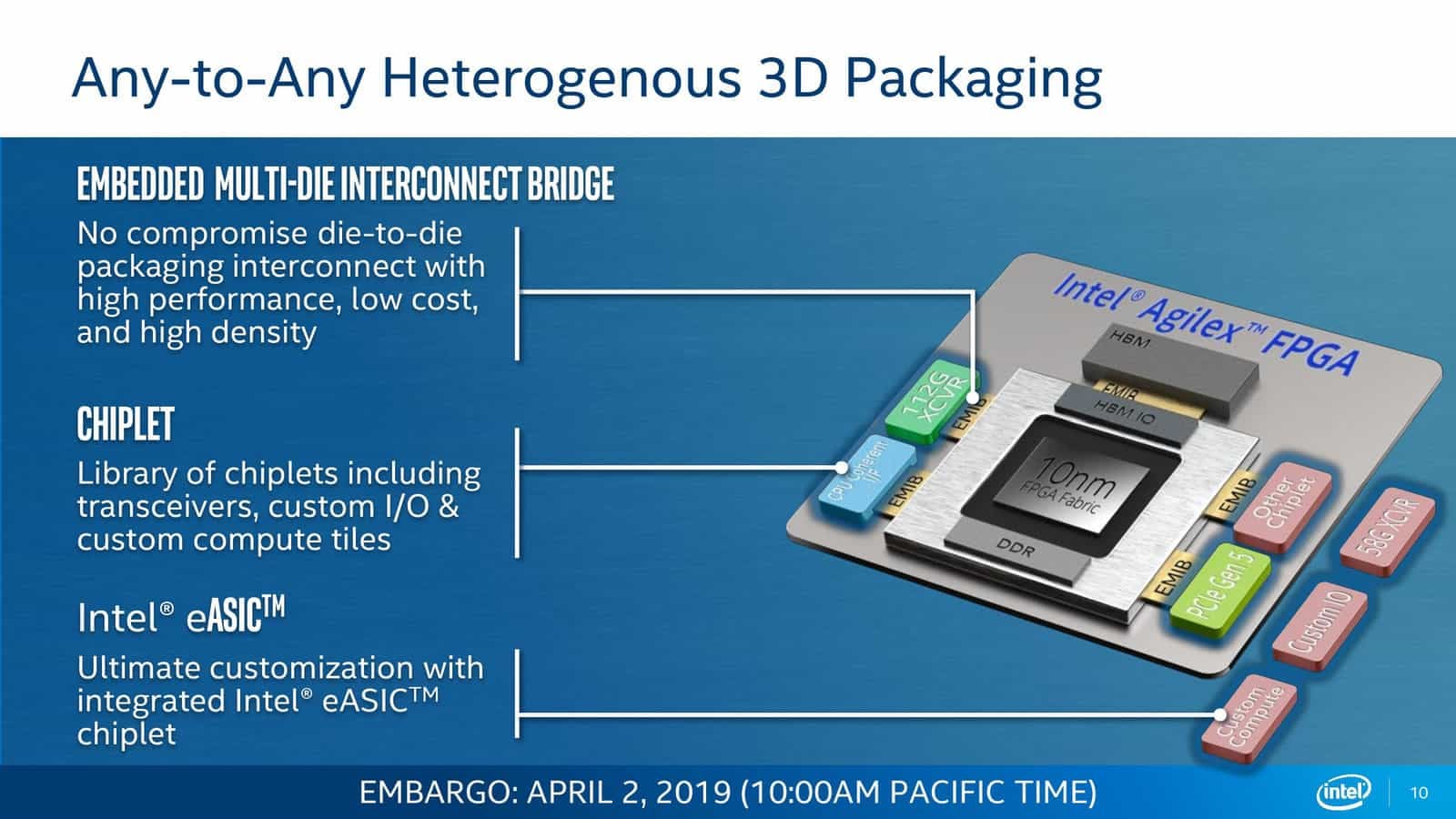

Agilex by měl v podstatě být první produkt, který je už plodem Altery po akvizici Intelem v roce 2015. Agilex přináší novou generaci proti současným čipům Stratix 10. Hlavní novinkou není jen výroba na 10nm procesu místo starého 14nm. Možná ještě důležitější může být pokročilé 2.5D pouzdření a další rozšířené možnosti. Agilex totiž není jen monolitický 10nm čip. Pomocí křemíkových můstků EMIB (které jsou alternativou křemíkového interposeru) mohou být k tomuto FPGA na jednom pouzdře připojené paměti HBM2 (podporuje však i DDR, a to včetně DDR5), ale zároveň může komunikovat s množstvím dalších čipletů.

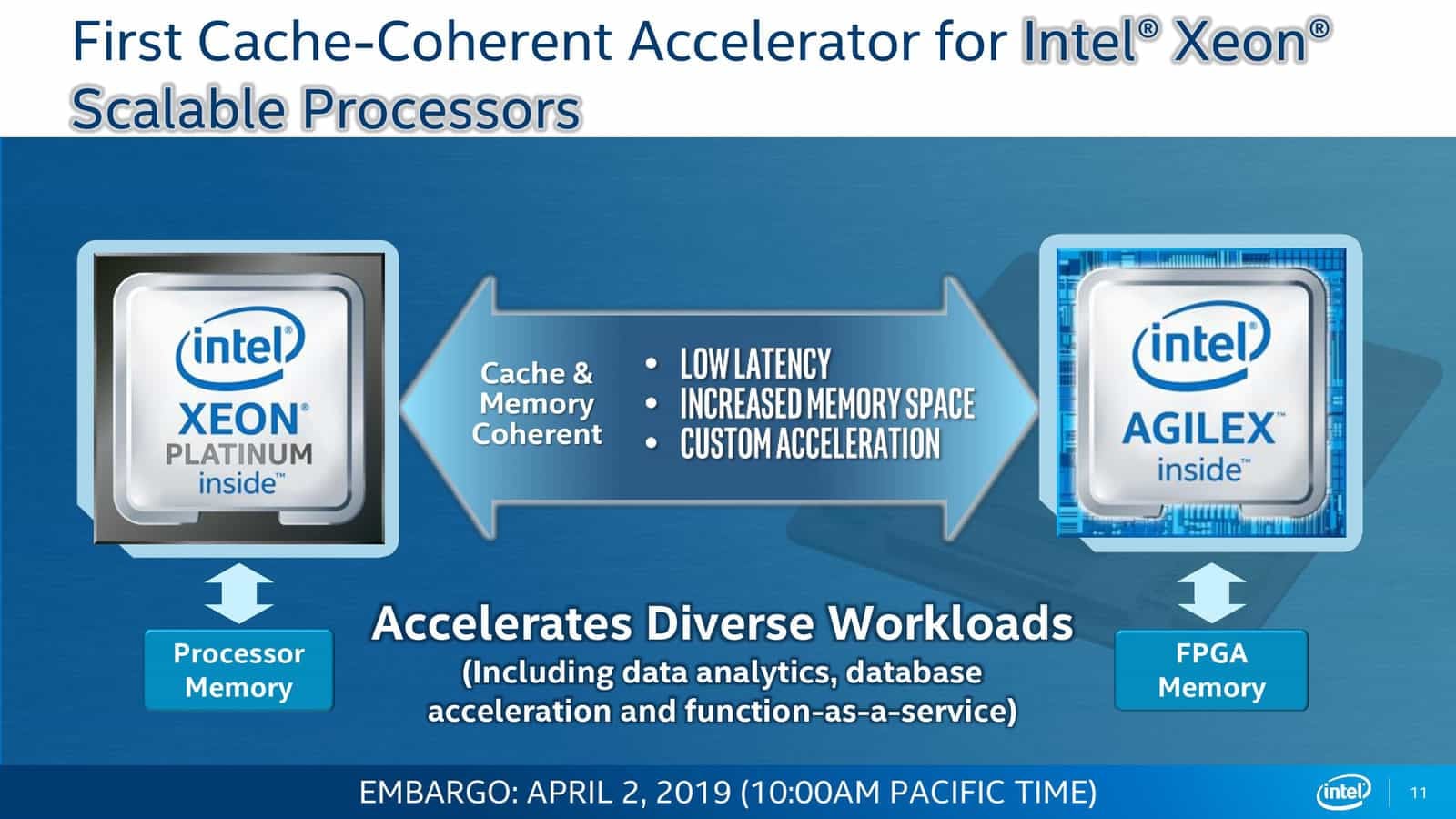

Přes EMIB a přídavné čipy Intel nabízí komunikaci přes rozhraní PCI Express 5.0, 112Gb/s transceivery (s nimiž se dá realizovat připojení na 100Gb/s Ethernet) a také koherentní připojení k procesoru, tedy se synchronizací cache a paměťového prostoru mezi CPU a FPGA. Tato komunikace bude používat koherentní protokol CXL, který Intel vyvinul na bázi právě PCIe 5.0. A kromě toho mohou přídavné čiplety pro toto FPGA být i zcela „custom“. Intel nebo jeho zákaznici je mohou vyvinout na míru klientovým potřebám.

Čiplety mohou přitom být heterogenní, vyvinuté na úplně jiném výrobním procesu. Intel toto přímo demonstroval se SERDES čiplety, které jsou údajně vyrobené na 16nm procesu TSMC. Zde by využití asi mělo být zejména v použití starších procesů pro analogové obvody a rozhraní (PHY), protože na těch je analogovou technologii často snazší implementovat.

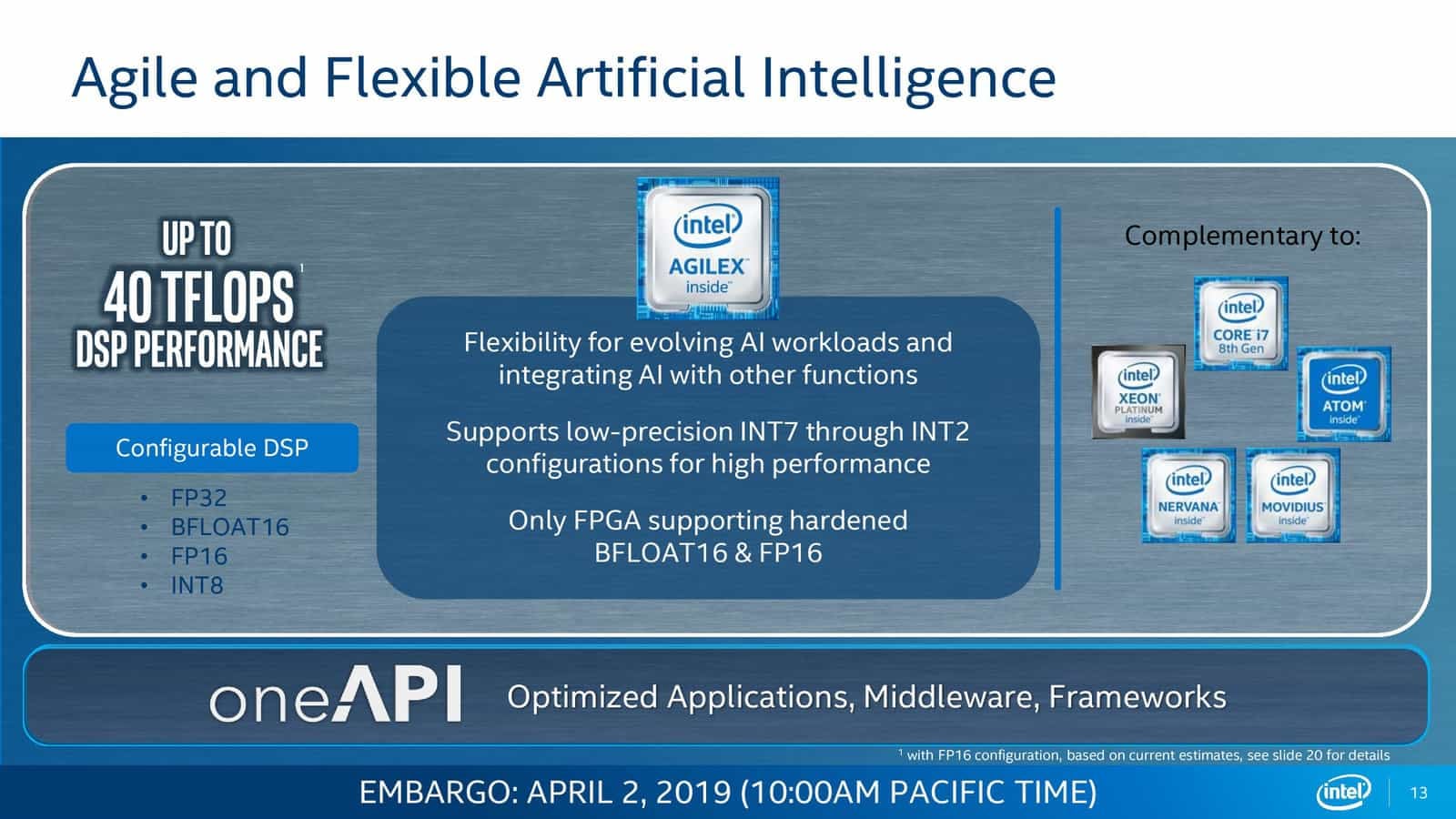

Výkon 10nm FPGA by přirozeně také měl být vyšší. Podle Intelu má mít až o 40 % vyšší potenciál nebo při stejném výkonu až o 40 % lepší spotřebu proti 14nm. Při implementaci DSP funkcí nad 16bitovými hodnotami (Bfloat16 nebo FP16) má být dosažitelný výkon až 40 TFLOPS. Intel bude Agilex nabízet v několika verzích. Základní verze F podporuje ještě jen PCI Express 4.0, paměti DDR4 a 58Gb/s transceivery. Náročnější verze I už má 112Gb/s konektivitu a podporu PCI Expressu 5.0 a podporu koherentního připojení ke Xeonům (patrně přes onen protokol CXL). Nejvyšší verze M podporuje kromě paměti DDR4 také HBM, DDR5 a také nevolatilní Optane DC Persistent Memory.

Reálná dostupnost bude až v druhé polovině roku

Na rozdíl od Xeonů Cascade Lake, které už před oznámením nějakou dobu byly pod pultem prodávány vybraným velkým klientům, ještě Agilex nebyl uveden natvrdo. Intel jej oznámil zatím jen předběžně. Dostupnost by měla začít od třetího kvartálu – zhruba ve stejné době, kdy mají přijít patrně i první 10nm procesory Ice Lake. Jako první má být dostupná verze F.

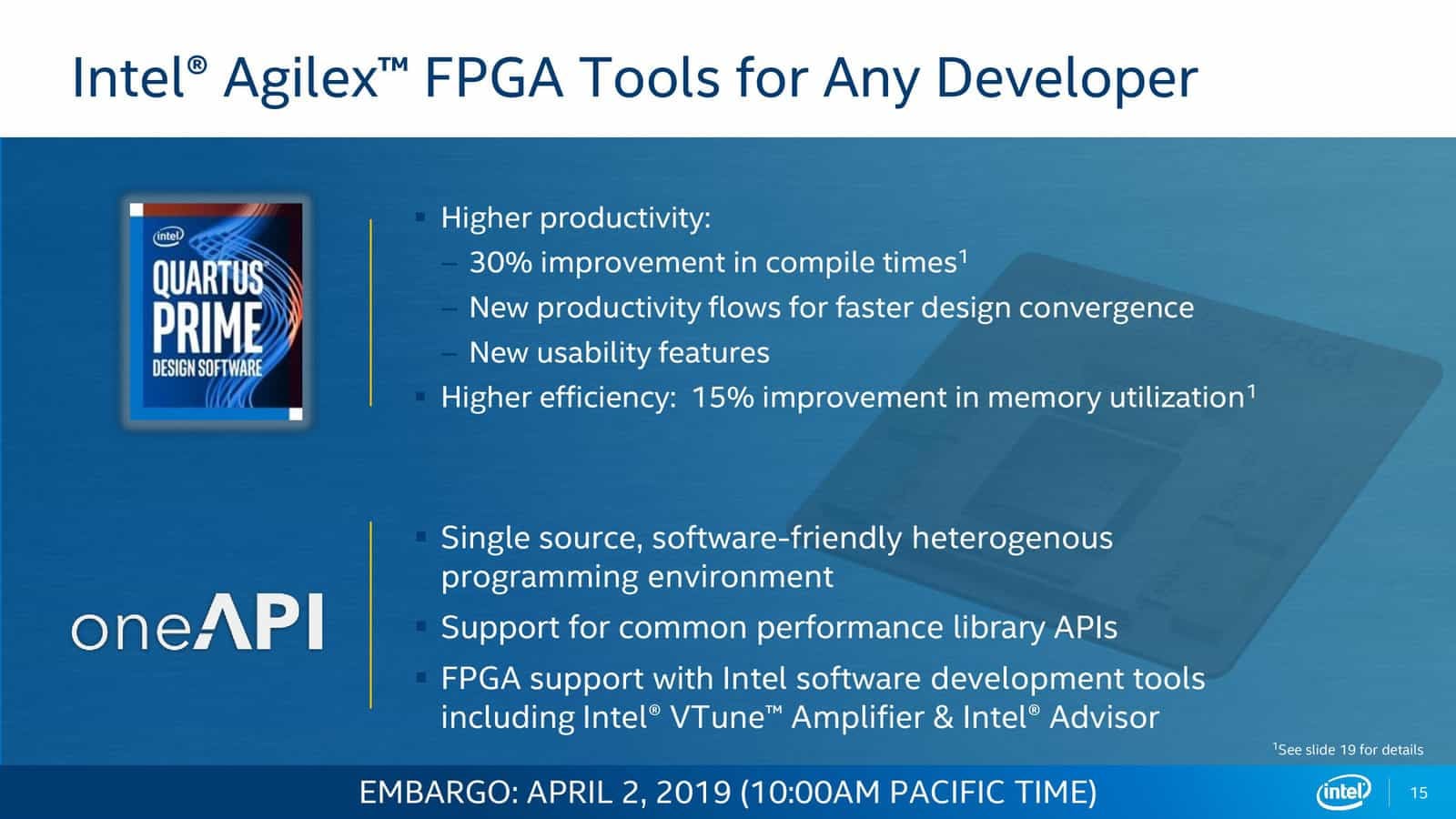

Prezentace: FPGA Intel Agilex