Konečně nová architektura CPU jader Intel: Sunny Cove

Architektura Sunny Cove je jádro, které přijde do procesorů Ice Lake – tedy druhé, „tock“ generace 10nm procesorů. Ovšem reálně vlastně první, protože Cannon Lake (10nm „tick“, byť s reálnými architektonickými zlepšeními) se víceméně ani nedostalo na trh.

Cove/Lake?

Cove/Lake?

Zde možná budou vznikat zmatky s kódovými označeními. Sunny Cove neznamená, že by se jednalo nějakou novou architekturu odlišnou od Ice Lake, jde jen o odlišné označení. V médiích se jádra ze zvyku označovala jménem celého čipu/SoC (tedy například Skylake, Kaby Lake), protože jsme pro ně od Intelu neměli samostatné jméno. Tato samostatná kódová označení přímo pro architekturu ale Intel interně používá a jsou to právě tato jména končící na Cove (zátoka). Nyní se s nimi zřejmě budeme setkávat i veřejně. Pamatujte si proto, že „Cove“ je vždy označení architektury jádra, kdežto „Lake“ je označení pro procesor, v kterém tato jádra budou integrovaná. Sunny Cove je tedy jádro uvnitř procesoru Ice Lake, jako má AMD jádra Zen+ v procesorech Pinnacle Ridge. Nebo Intel u Atomů, kde se procesor jmenuje např. Gemini Lake, ale samotné jádro má označení Goldmont+.

Sunny Cove: vyšší IPC, větší cache

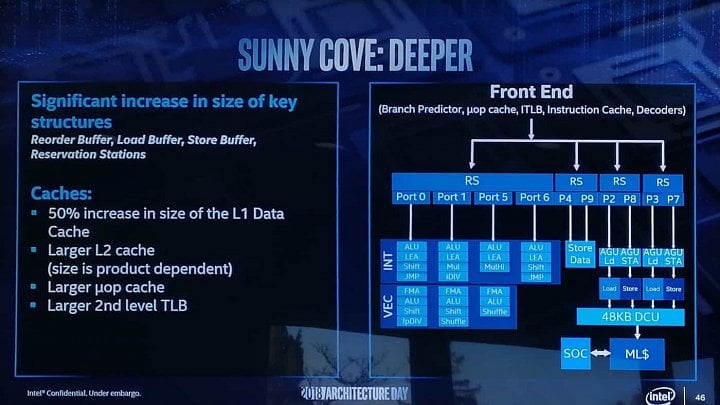

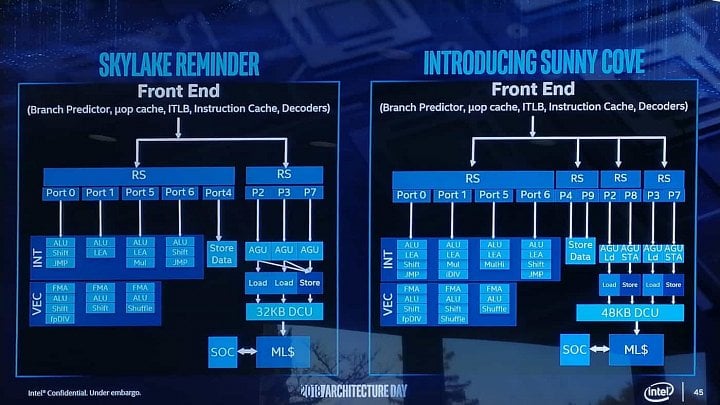

Sunny Cove je první „tock“, tedy nová či lépe řečeno silně přepracovaná architektura, od Skylake. Jak už chvíli víme, Ice Lake (tedy Sunny Cove) dostane změněné cache. To se nyní potvrzuje. L1 cache pro data je nově 48KB (zvětšení o 50 %) a L2 cache bude také zvětšena. Ovšem pozor, ne vždy to musí být na 512 KB, které ukazovaly úniky. Intel uvádí, že velikost může záviset na produktu, takže je možné, že v některých segmentech trhu může být větší (servery).

Kromě hlavních cache ale jádro zvětšilo také TLB druhé úrovně a pozor, také „L0“, respektive „uOP cache“. Ta měla dosud 2048 položek, nyní to bude víc, ale přesně nevíme (shodou okolností je toto zlepšení, které bude paralelně aplikovat i Zen 2 od AMD). Větší cache znamenají, že procesor v nich častěji najde data a zkrátí si čekání na vyhledání v RAM. Větší uOP cache zase znamená, že procesor častěji najde dekódované instrukce v ní a vyhne se použití energeticky náročných dekodérů, které jsou zároveň často tzv. úzkým hrdlem výkonu.

Víc portů, druhá míchačka pro SIMD

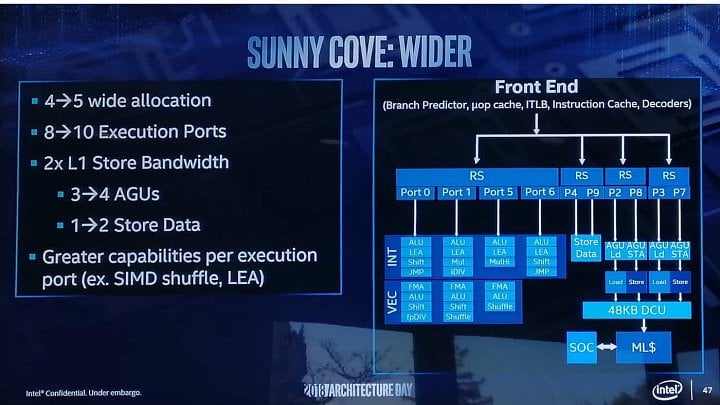

Jádro bude celkově širší. Issue/retire se zvýší ze čtyř na pět instrukcí za takt. A současně Intel zvedl počet portů, na které se dělí výpočetní jednotky v jádře na deset z osmi. Nové porty P8 a P9 přibudou v load/store části procesoru a zvýší tak kapacitu pro načítání dat z paměti a jejich ukládání. Sunny Cove/Ice Lake díky nim bude schopné provádět dvě čtení a zároveň dva zápisy do paměti. CPU bude mít čtyři AGU místo tří a kapacita ukládání se tímto zdvojnásobila proti Skylake. to umí dvě čtení a jedno ukládání. Pro srovnání, Zen umí jen dvě načítání, nebo dvě ukládání, pokud se tedy tyto operace stanou úzkým hrdlem, má o dost nižší kapacitu.

U přímo výpočetních jednotek ALU/FPU je to méně vidět, ale i zde došlo ke změnám. Jejich čtyři porty mají lepší schopnosti. Například všechny porty umí instrukce LEA (dříve jen dva), násobení budou umět dva porty jednotky místo jednoho. Na těchto stejných portech (respektive třech z nich) má Intel jako dosud navěšené také jednotky FPU/SIMD. Hlavní zlepšení by v jejich případě mělo být v tom, že nově umí operace Shuffle dvě jednotky místo jediné: porty 1 a 5. Toto bylo slabé místo, protože port s instrukcemi shuffle býval v SIMD kódu přetížený (zvlášť s AVX-512), takže zdvojení jednotky shuffle by mělo zlepšit výkon SIMD operací například v multimédiích. Intel měl dvě jednotky shuffle už dřív do architektury Sandy/vy Bridge, ale Haswell a Skylake ji obětovaly. Takže zde jde vlastně o návrat, který si údajně přímo vyžádali zákazníci/programátoři.

Hlubší fronty a další...

Kromě těchto úprav zlepší výkon (IPC) v již existujícím kódu ještě další věc. Intel uvádí, že byly zvětšeny buffery spojené s out-of-order vykonáváním operací, čímž by CPU mělo být schopno optimalizovat provádění lépe, jelikož má pro něj větší „okno“, vidí delší část kódu. Zvětšen byl Reorder Buffer, fronty Reservation Stations jednotlivých portů a také fronty čtení z paměti a ukládání do paměti. Není ale řečeno, o kolik, či jak budou u Sunny Cove hluboké. Kromě toho byla také prý snížena celková latence načítání dat (ovlivňovaný L1 cache a TLB) a také byl opět vylepšen prediktor větvení.

S tím souvisí, že jádro by mělo mít nové opravy proti útokům typu Spectre na spekulativní vykonávání kódu, jakož i opravy, které už jsou v posledních 14nm architekturách. Bezpečnost by také měla zlepšovat rozšíření umožňující šifrování paměti (Total Memory Encryption) a zabránění vykonávání instrukcí v usermode režimu. Paměťový řadič bude jinak také podporovat více bitů adresního prostoru, až 57 lineárního adresování. Fyzický adresní prostor bude zvětšen na 52 bitů.

Sunny Cove: nové instrukce a schopnosti

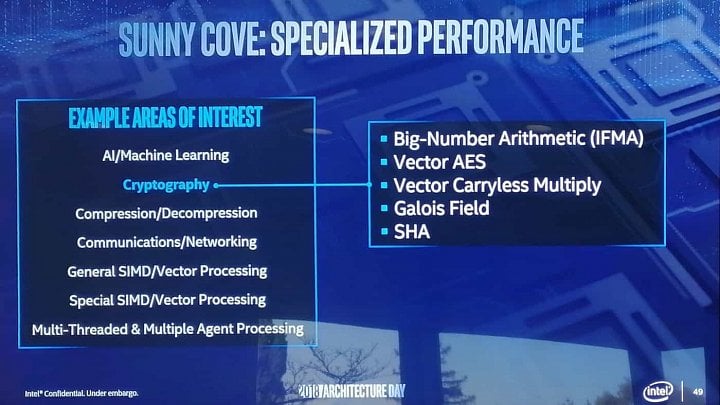

Kromě architektonických změn, které budou obecně zlepšovat ICP plus minus všude, bude mít nové jádro také zlepšení jako jsou nová instrukční rozšíření, která také zlepší výkon, ale jen tehdy, pokud je programátoři využijí. Zaměřená budou na SIMD instrukce, strojové učení, kryptografii a podobné účely.

Sunny Cove bude jako jádro Cannon Lake podporovat instrukce AVX-512, byť spotřebitelská verze asi s nižším výkonem než Xeony (pro 512bitové operace budou pravděpodobně kombinovány 256bitové jednotky FMA na portu 0 a 1, nebude přítomna další samostatná 512bitová FMA). Sunny Cove přidá také podporu pro instrukce IFMA které se hodí pro aritmetické a kryptografické operace. A nově se objeví také vektorové instrukce pro šifrování (AES, SHA, bezpřenosové násobení/CLMUL, instrukce pro operace Galoisových těles).

Výkon zatím není jasný, ale IPC by mohlo být o hodně lepší

Celkový dopad těchto změn na IPC nelze bohužel dost dobře předpokládat, takže vám nemůžeme předhodit nějaký odhad, o kolik procent vzroste výkon jader Sunny Cove v Ice Lake proti stejně taktovanému Skylake. Tipnul bych si, že by mohlo by jít aspoň o 10–15 %, ve speciálních případech (SIMD) ale i více. Neznáme ale, na jakých frekvencích tyto už 10nm čipy poběží, takže výkon lze odhadovat dost těžko. Intel však uvádí v roadmapě, že očekává zvýšení jednovláknového výkonu coby jedno z hlavních zlepšení, což by naznačovalo signifikantní zlepšení IPC.

Článek pokračuje na další straně informacemi o plánech Intelu na následující generace procesorů a tom, kdy se Sunny Cove objeví na trhu.

Roadmapa Intelu na roky 2019 až 2023: po architektonickém suchu přijdou povodně

Na začátku bylo zmíněno, že Intel kromě Sunny Cove avizoval i další, následující jádra. Firma totiž ukázala roadmapu s určitými podrobnostmi i pro další následníky. Ta je označena roky a zdá se, že v následujících letech by nová jádra měla přicházet v rychlém sledu. Dojde tak zřejmě na úplné obrácení nynější situace, kdy jedno jádro Skylake musí vystačit na nějaké čtyři roky, pokud ne déle. Je to asi proto, že odklad 10nm procesu způsobil i odklad architektur, které ale byly vyvíjeny bez ohledu na to. Až tedy Intel 10nm proces konečně uvede do provozu, bude mít takříkajíc zásobu jader blízkých dokončení v šuplíku a nové architektury tedy budou naopak moci vycházet se zvýšenou kadencí. Následující léta tedy asi budou k upgradu zajímavější, než ta nynější.

V roadmapě je Sunny Cove zařazeno na rok 2019 (pravděpodobně jeho konec). První procesory Ice Lake by tedy měly vyjít na konci příštího roku, ale dost možná to bude jen v některých segmentech trhu. Připomeňme, že nedávno prosáklá roadmapa NUCů mluví o šestijádrových 14nm procesorech Comet Lake-U pro notebooky a přijde také desktopový Comet Lake- s 10 jádry, takže první Ice Lake asi budou promíchány s 14nm produkty, které nahradí nové 10nm architektury až později v roce 2020.

Willow Cove: Mesh?

Po Sunny Cove má přijít jádro označené Willow Cove a nyní plánované snad na rok 2020 (i když by to opět mohlo být na jeho sklonku). Toto jádro by snad mohlo pohánět procesory Tiger Lake stále na 10 nm procesu. Oproti 14nm „optimalizaci“ Kaby Lake to tentokrát bude vylepšené jádro. Intel o něm uvádí, že má mít zlepšení v oblasti bezpečnosti a také vylepšený výrobní proces. A konečně také „redesign cache“. To je zajímavé, protože jak víme, Sunny Cove mělo samo změnu v L1 i v L2 cache, takže by se čekalo, že se s nimi nebude hned šachovat znovu. Zvlášť když by Willow Cove asi mělo být méně radikální a více evoluční proti Sunny Cove. Není totiž explicitně zmíněno zlepšení jednovláknového výkonu.

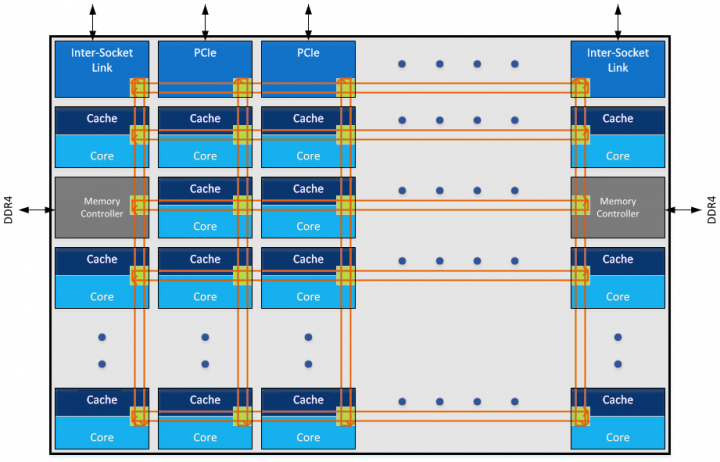

Nabízí se myšlenka, že by se pod tímto heslem mohlo myslet překopání L3 cache. Jako „cache redesign“ myslím Intel označoval změny L3 cache na exkluzivní s tím související přechod od prstencové sběrnice k mesh uspořádání jader v Skylake-X a Skylake-SP. Je proto možné, že nucen zvyšujícím se počtem jader Intel s architekturou Willow Cove zavede mesh propojení také u běžných mainstreamových procesorů Tiger Lake-S (a možná i mobilních Tiger Lake-U/Y).

Golden Cove: druhý 10nm tock?

Poslední generace prozrazená pro velká jádra Core je Golden Cove. Pro tu Intel uvádí jako zlepšení „jednovláknový výkon“, což by mohlo znamenat, že zde opět přijdou výrazné změny (mohlo by opět jít o „tock“) a tím velké zlepšení IPC. Toto jádro by mohlo přijít do procesorů Alder Lake, ale asi ještě stále půjde o 10nm čipy. Jako další zlepšení jsou uvedená zlepšení výkonu v „AI“, což by mohlo znamenat nějaká SIMD rozšíření pro strojové učení (třeba rozšíření VNNI, které má Cascade Lake, nebo instrukce z procesorů Xeon Phi Knights Mill). A konečně má Golden Cove/Alder Lake opět přinášet zlepšenou bezpečnost. Toto jádro Golden Cove patrně přijde někdy v roce 2021.

Zajímavý detail je jinak toto: Intel uvedl, že v budoucnu už architektury jádra nebudou těsně spjaté s výrobním procesem, pro který byly vyvíjeny. Toto je velká změna a měla by předejít problémům z dneška, kdy opoždění 10nm výroby znemožnilo Intelu využít zlepšení, která vyvinul pro Cannon Lake a Ice Lake. V budoucnu by architektura v podobných problémech tedy asi mohla být přenesena zpátky na předchozí odladěný proces. To sice může omezit její potenciál, ale v případě, kdy by se opět opozdil třeba 7nm nebo 5nm proces, může Intel aspoň nasadit novější architekturu a přinést tak určitý pokrok a nové funkce i bez nového procesu.

Ocean Cove až později

Zajímavý detail je, že v této roadmapě není vidět jádro Ocean Cove, o němž se objevily informace už v dřívější době. To by mohlo znamenat, že tato architektura (údajně výrazně inovované a možná vzniklá po dlouhé době na úplně novém základu) přijde až poté, někdy v roce 2022 nebo později a už na 7nm procesu. Snad v procesorech označených Meteor Lake. Ale tato architektura zatím ještě ve veřejné roadmapě není.

Roadmapa Atomů: malá jádra jedou dál

Současně Intel ukázal i roadmapu Atomů, kde ale budou nová jádra přicházet s méně frenetickou frekvencí. Patrně v roce 2019 přijde architektura Tremont na 10nm, o které už chvíli víme. Jde zřejmě o „tock“, zvyšující IPC. Intel totiž uvádí zlepšení jednovláknového výkonu. Současně mají být čipy s jádry Tremont úspornější a také mají mít lepší výkon při použití v serverových/síťových procesorech.

Po Tremontu je další nové jádro Atom plánováno asi v roce 2021 pod označením Gracemont. Opět má zlepšit jednovláknový výkon, a tedy asi IPC: Ale Intel zmiňuje také, že tyto procesory dosáhnou také vyšších frekvencí. Pravděpodobně ale asi ještě stále budou 10nm. Zajímavé je ještě, že mají mít lepší výkon instrukcí SIMD. Je možné, že jim Intel rozšíří výpočetní jednotky, teoreticky by možná mohly dostat podporu instrukcí a registrů AVX/AVX2.

Někdy v letech 2022 či možná spíš 2023 má pak následovat třetí nové jádro Atom, zatím beze jména, označené jen „Next Month“ (což je asi překlep). Podrobností je málo. Jádro má mít nové funkce, ale opět také vyšší frekvence i vyšší „jednovláknový výkon“. Protože tyto položky Intel uvádí jako dvě různé věci, patrně se pod vyšším „ST výkonem“ opět míní zlepšení IPC. Atomy založené na této architektuře by už asi mohly být vyráběné na 7 nm.

Je zajímavé, že Intel ukázal roadmapu Atomů dále do budoucnosti. Ukazuje to mimo jiné, že druhá menší architektura zůstává integrální součástí plánů Intelu a zatím nejsou žádné plány ji opustit – jako to udělalo AMD, když přestalo vyvíjet linii malých jader Bobcat/Jaguar a Zen musí posloužit pro pokrytí celé šíře použití. To však dost možná bylo dáno pouze financemi, s kterými Intel problémy ani zdaleka nemá.

Je zajímavé, že Intel ukázal roadmapu Atomů dále do budoucnosti. Ukazuje to mimo jiné, že druhá menší architektura zůstává integrální součástí plánů Intelu a zatím nejsou žádné plány ji opustit – jako to udělalo AMD, když přestalo vyvíjet linii malých jader Bobcat/Jaguar a Zen musí posloužit pro pokrytí celé šíře použití. To však dost možná bylo dáno pouze financemi, s kterými Intel problémy ani zdaleka nemá.