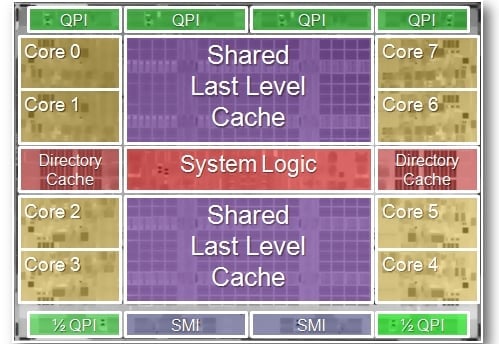

Na architektonickou inovaci Itania je již nejvyšší čas. Čtyřjádrová Tukwilla, vyráběná ještě 65nm procesem, už na trhu bojuje druhým rokem. Nová architektura Poulson je poměrně radikálním vylepšením. Nový (ačkoliv ne nejnovější) výrobní proces umožnil zvětšit počet jader na osm. Schéma procesoru ukazuje, že jsou podobně jako u Xeonů umístěna po okraji čipu a propojena centrální prstencovou sběrnicí. Itanium Poulson dokáže v každém procesorovém jádru zpracovat dvě vlákna, podobně jako je tomu u technologie HyperThreading v čipech x86.

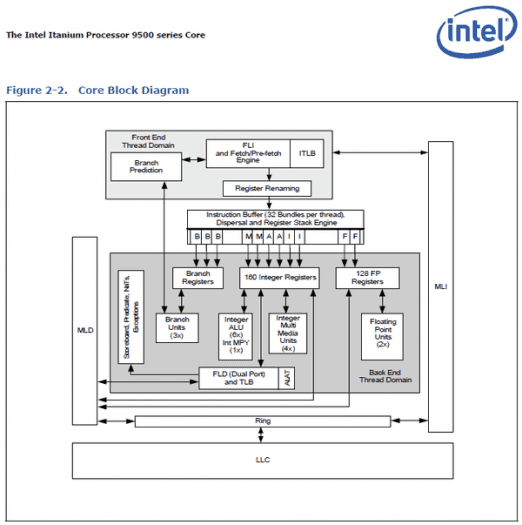

Procesory Itanium používají architekturu VLIW. Instrukce jsou procesoru předkládány v balíčcích po třech. Zatímco starší procesory zvládaly v jednom taktu dva balíčky, tedy 6 instrukcí, Poulson má dvojnásobnou kapacitu. Za takt zvládne instrukcí 12 (je tedy „12-issue“). Stále se ovšem jedná o zpracování typu in-order (podobně jako například v Atomu). Nevýhody této architektury jsou však zmírněny zpracováváním dvou vláken najednou a také bufferem o kapacitě 96 instrukcí (pro každé vlákno), který pohltí například prodlevy způsobené čekáním na data.

Vzhledem k širokému „front-endu“ čipu nepřekvapí, že jádro disponuje poměrně velkým počtem výpočetních jednotek. K dispozici je 6 ALU, 4 jednotky pro zpracování instrukcí SIMD, 2 jednotky pro paměťové operace a 2 FPU. Následuje jedna jednotka pro celočíselné násobení a 3 jednotky pro zpracování větvení. Jádro navíc odděleně zpracovává instrukce NOP, aniž by došlo k zaměstnání výpočetní jednotky. To je důležité proto, že architektura VLIW používá tyto „operace“ k zaplňování nevyužitých pozic v instrukčních balíčcích. Pipeline procesoru má 11 stupňů (pro FPU je to o 6 stupňů více).

Poulson má větší počet registrů, proti předchůdci jich přibylo rovnou 32 a celkový počet obecných registrů je tedy 128. Dále má procesor vylepšené přednačítání dat, a to jak po hardwarové, tak po softwarové stránce. Tyto změny jsou částečně vynuceny tím, že procesor musí paralelně zpracovávat více instrukcí. Zároveň by ale měly dále zvýšit výkon za takt.

Procesory se na trhu objeví pod označením Itanium 9500. Manuál zmiňuje čtyři modely, očíslované 9520, 9540, 9550 a 9560. Jejich konfigurace není specifikována, dle serveru CPU World však poběží na značně vyšších frekvencích než Tukwilla, která končila na 1,73 GHz. U Poulsonu bude prý takto taktován základní model 9520. Model 9540 pak poběží na 2,13 GHz, 9550 na 2,4 GHz a vrchol nabídky, model 9560 na 2,53 GHz. Co se týče paměti cache, dle The Registeru by se mělo jednat o 32 MB sdílené L3 a 6 MB L2 cache (ta je rozdělena na 2 MB pro data a 4 MB pro instrukce). L1 cache má pak v každém jádře 16 kB pro data a stejně tolik pro instrukce.

Ačkoliv na papíře může Poulson vypadat působivě, nelze zapomínat, že procesory architektury x86 se vyvíjejí ještě rychleji. Vzhledem k tomu, že Poulson má opět zůstat na trhu zhruba dva roky, může v budoucnu výkonově poměrně značně zaostávat. Atraktivitě také procesorům nepřidává nejistota kolem softwarové podpory, která je dokonce předmětem soudních sporů. Kromě společnosti HP totiž nezbývá mnoho firem, které by za architekturou stály. Již nyní Itanium sdílí infrastrukturu (například sběrnici QPI) s Xeony a v budoucnu jimi asi bude i zcela nahrazeno.

Zdroje: Intel, The Register, CPU World