Už jsme tu chvíli neměli zprávu o tom, co se v budoucnu má dít v oblasti procesorů (míněno těch pro PC s architekturou x86). Shodou okolností se ale zrovna sešlo několik takových zpráv, týkajících se „modrého tábora“ (tedy produkce firmy Intel), a tak můžeme toto téma zase jednou otevřít. Na začátek bude možná dobré zrekapitulovat, co vlastně o budoucích plánech Intelu nyní víme nebo „známe“ z úniků. Čerstvě uvedené procesory Coffee Lake na desktopu a 10nm čipy Cannon Lake (měly by vyjít koncem roku nebo někdy během roku 2018) představují v roadmapě jednu generaci, která by původně byla 10nm „dieshrinkem“ čili „tickem“, následujícím „tock“ Skylake, tedy novou architekturu. Mezi tock a tick se nyní v novém modelu „PAO“ (proces – architektura – optimalizace) dostává ještě jedna „vycpávková“ (berte s nadsázkou) generace, což byly letos na 14nm procesu čipy Kaby Lake. Každopádně Coffee Lake a Cannon Lake jsou koncem aktuálního cyklu, který začal se Skylake a na desktopu používal platformu LGA 1151. Po těchto čipech by měl začít nový cyklus s novou procesorovou architekturou a platformou.

Na řadě: Ice Lake, Tiger Lake, (???), Sapphire Rapids

Co bude následující nová architektura („tock“) v novém cyklu, už také víme: jde o čipy Ice Lake, které přinesou druhou generaci 10nm procesu („10nm+“), tentokrát snad už i na desktop. Hlavní u nich ale bude ona nová architektura CPU. Také po Ice Lake má přijít nová generace, která nebude mít velké změny ani nový proces, jelikož 7nm výroba ještě nebude připravená. Tyto čipy, které budou ekvivalentem Kaby Lake v 10nm cyklu, se mají nazývat Tiger Lake. Má-li Ice Lake být uvedeno v roce 2019, pak Tiger Lake by patrně měl být na prodej v roce 2020 (ale je možné, že Ice Lake to stihne koncem roku 2017, pak by se i následníci mohli posunout dopředu). Ice Lake a Tiger Lake by měly používat novou platformu základních desek, která by neměla být kompatibilní s nynějším socketem LGA 1151, jelikož platformu Intel vždy s novou architekturou CPU jádra vymění a Ice Lake údajně má používat opět integrovaný regulátor napětí jako Haswell a Broadwell, což by bylo určitě nekompatibilní se současnými deskami.

Aktualizováno (15. 10. 2017): Tiger Lake podle Ashrafa Eassy nemá být úplně jako Kaby Lake. Údajně by mělo mít proti Ice Lake aktualizované GPU na architekturu Gen12. Na rozdíl od Kaby Lake, přidaného do plánů poměrně pozdě, měl Intel na vývoj tohoto CPU pravděpodobně více času, tudíž by jeho součástí mohlo být více nových či aktualizovaných komponent, i když stále asi nelze čekat radikální změny, jelikož jde o fázi "optimalizace" a architektonický "tock" přinese Ice Lake před ním.

DDR5 ještě dlouho nebude

DDR5 ještě dlouho nebude

Tolik tedy rekapitulace a nyní nové informace. Ashraf Eassa z investičního webu Motley Fool tento týden publikoval na Twitteru několik věcí, které zdá se zjistil v nějakých dokumentech Intelu. První z nich je, že jak Ice Lake, tak Tiger Lake budou stále používat paměti DDR4, případně v mobilním segmentu LPDDR4. Ani Tiger Lake údajně ještě nebude podporovat novou generaci operačních pamětí DDR5. Pro tu tedy asi nastane čas nejdříve v následující generaci, která by snad měla vyjít v roce 2021 (pokud očekáváme roční rozestupy). Nicméně ani pro tu to nemáme konkrétně potvrzeno.

Sapphire Rapids, nová architektura?

Jak se bude jmenovat tato následující generace? V období po Tiger Lake známe zatím jedno jméno, které je dokonce i oficiálně potvrzeno. Na webu Intelu se dá najít kódové označení „Saphire Rapids“, které podle všeho označuje následující generaci procesorů/CPU architektury – nebo jednu z následujících generací. Není totiž jasné, zda jde ještě o posledního třetího člena cyklu začínajícího procesory Ice Lake, nebo už o novou architekturu CPU, která by začínala vlastní zhruba tříletý cyklus. Změna stylu označení (peřeje místo jezer) by teoreticky mohla znamenat, že už jde zase o novou architekturu. To by pak ale asi také znamenalo, že mezi Sapphire Rapids a Tiger Lake by se mohla vtěsnat ještě jedna generace se zatím neznámým jménem, tedy nějaké první 7nm čipy, představující „dieshrink“ Ice Lake/Tiger Lake. Pokud by byl procesor Sapphire Rapids nová architektura, byl by patrně také už na 7nm procesu, pakliže se tedy Intelu neopozdí vývoj výrobních technologií a nebude třeba CPU portovat zpět na pozdní variantu 10nm procesu coby plán B (jako u Coffee Lake).

Serverová oblast

Serverová oblast

To, že by Sapphire Rapids teoreticky už mohly být zase procesory s úplně novou architekturou jader, naznačuje ještě jedna věc (připomeňme, že někde zde v budoucnosti by Intel pravděpodobně mohl nasadit něco radikálně nového, pokud drby nelžou). Spolu s jádry Sapphire Rapids by se totiž měla objevit také nová serverová platforma a patrně také asi nový socket. Tato platforma se údajně jmenuje Tinsley a má být podobným předělem jako letošní uvedení Skylake-SP a jeho socketu LGA 3647. Na této nové platformě a serverové verzi čipů Sapphire Rapids by dost možná už mohly fungovat paměti DDR5.

Předtím by měla vyjít ještě serverová platforma Whitley, která ale asi bude jen evolucí té současné (nazvané Purley), tedy se stejným socketem a asi i kompatibilitou. K platformě Whitley by patrně měly patřit serverové procesory odvozené od Ice Lake, předtím ale má Intel uvést ještě čipy Cascade Lake, které by zdá se mohly být refreshem Skylake-SP. Bohužel neznáme časový horizont, v kterém by tyto novinky mohly přicházet, Cascade Lake by ale snad mohlo vyjít příští rok.

Serverové čipy Ice Lake přijdou na platformu Whitley. Čipset je zdá se stále Lewisburg, tedy stejný jako pro Skylake-SP

Serverové čipy Ice Lake přijdou na platformu Whitley. Čipset je zdá se stále Lewisburg, tedy stejný jako pro Skylake-SPPředchozí se ovšem týká jen velkých serverových CPU. Kromě těch Intel ale bude nadále vyvíjet i menší Xeony D, které jsou více integrované a fungují jako SoC s nižší spotřebou v BGA pouzdru. Příští generace Xeonu D má kódové označení Bakerville. Podle Eassy jde asi stále ještě o 14nm čipy, protože mají být ještě odvozené od architektury Skylake. Nebudou tedy představovat nějaký raný výskyt 10nm procesu nebo dokonce nové procesorové architektury. Proč uvedení Xeonů D s těmito jádry trvalo tak dlouho (Skylake pro PC byl uveden už před dvěma lety), netušíme. Je možné, že v této oblasti Intel necítil velký tlak a proto raději šel cestou vývoje Xeonů D s vyšším počtem jader a stále architekturou Broadwell.

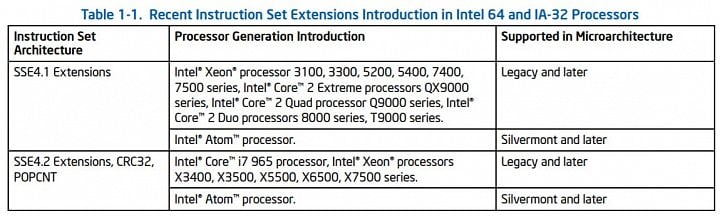

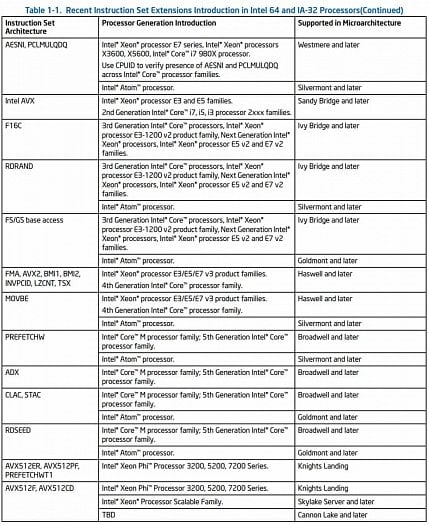

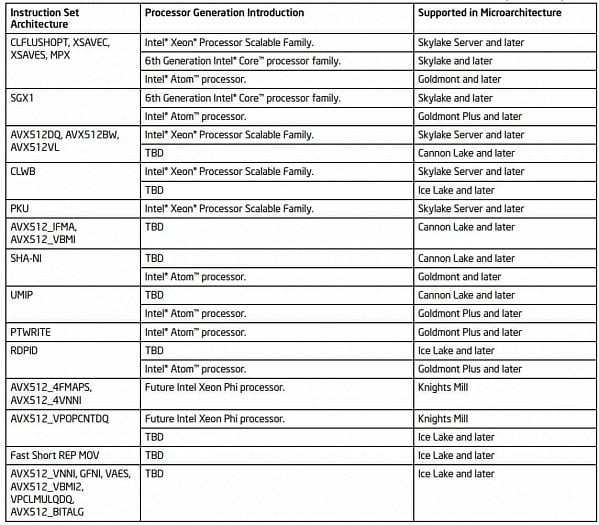

Instrukční sada (sady) AVX-512 se bude rozrůstat

Pokud jste programátoři, pak vás asi bude zajímat, že Intel má naplánovánu poměrně velkou expanzi instrukčních rozšíření „AVX-512“. To je zatím přítomno jenom v Xeonech Phi, Xeonech generace Skylake-SP/Skylake-W a v procesorech Skylake-X pro platformu X299. Aktuální verze manuálu Intel Architecture Instruction Set Extensions and Future Features Programming Reference ale zdá se ukazuje, že tyto instrukce by se zřejmě měly dostat i do běžných „klientských jader“.

V tabulce, která jednotlivá rozšíření vypočítává, se totiž u řady těchto instrukcí objevuje, že budou podporována v čipech „Cannon Lake a pozdějších“ a nemělo by jít o jejich serverovou verzi, protože tu Intel odlišuje („Skylake Server“). První čipy Cannon Lake – paradoxně mobilní řada Y, určená pro pasivní notebooky a výkonné tablety – by měly vyjít během pár měsíců, takže by přítomnost AVX-512 mohla být potvrzena relativně brzy.

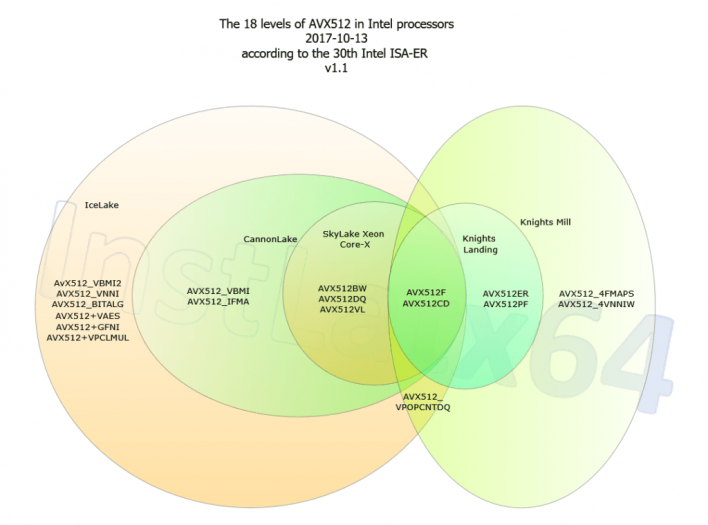

Rozšíření AVX-512 je dle tohoto dokumentu skutečně hodně – přičemž některá má přinést až Ice Lake – vidět je můžete v tabulce a v množinovém grafu, který vytvořil twitterista InstLatX64. Napříč čipy Skylake-SP/W/X, Xeon Phi Knights Landing, Knights Mill (zvláštní verze pro strojové učení), Cannon Lake a Ice Lake bude existovat několik různých podmnožin, které CPU může podporovat. Programátoři tedy budou muset hodně řešit kompatibilitu, pokud je pro nějaký kód budou chtít použít, což se naštěstí dá řešit i runtime detekcí přímo v programu, kdy binárka zvolí optimální kód automaticky. Tato fragmentace ale mezi vývojáři asi nebude úplně populární; doufejme, že je neodradí od jejich použití.

Je ještě třeba upozornit, že kompatibilita s AVX-512 nemusí nutně znamenat, že čipy Ice Lake a Cannon Lake budou s těmito instrukcemi mít plný výkon. V některých případech by totiž teoreticky mohlo dojít na to, že se pro 512bitové vektory budou požívat 256bitové jednotky pro AVX/AVX2, čímž by se výkon s těmito instrukcemi nezvyšoval.