Podobně jako před vydáním předchozích architektur začalo totiž AMD zasílat do různých softwarových nástrojů (v tomto případě GNU Binutils) patche, které specifikují, jaké instrukce bude nová architektura umět. Díky tomu, že jde o projekty typu open source, se tím tyto informace také dostávají na veřejnost. Zen se v kódu Binutils (a později zřejmě i dalších projektů) označuje Znver1, což naznačuje, že po jeho první generaci přijdou podobně jako v rodině stavebních strojů další evoluční následovníci. Patch si můžete prostudovat zde, v tuto chvíli by již měl být i začleněn.

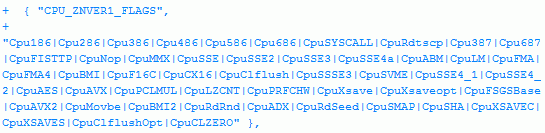

Pro nás je nejzajímavější to, co přibylo v souboru /opcodes/i386-gen.c. Zde jsou specifikována instrukční rozšíření, které má Zen (verze 1) umět a lze je též srovnat se sousedícími položkami pro Steamroller a Excavator (Bdver3 a Bdver4). Ve všeobecnosti lze říci, že novinka bude umět skoro vše, co tyto architektury, ovšem ne úplně všechno. Některé instrukce naopak zmizí. Na oplátku dostane Zen i nějaké novinky.

Instrukční rozšíření platná pro architekturu AMD Zen dle kódu GNU Binutils

Nic se nemění na podpoře hlavních instrukcí SIMD jako MMX, SSE-SSE4 a AVX, přibude k nim ale rozšíření AVX2 (které by ale prý měl umět již Excavator). AVX2 je docela zásadní rozšíření pro optimalizaci multimediálního kódu, slušných zrychlení s ním lze dosáhnout například v x265. Zatím ale není jasné, zda bude mít Zen nativní 256bitové vektorové jednotky – pokud by totiž měl jako Bulldozer jen 128bitové, velké zrychlení se konat nebude. 512bitové AVX-512 naopak Zen zatím mít nemá. Přírůstkem oproti aktuálnímu Steamrolleru bude též BMI2, což jsou instrukce zavedené Haswellem.

Zajímavé je, že Zen bude zřejmě podporovat akceleraci kryptografického algoritmu SHA, s níž má na straně Intelu přijít Cannonlake, to ale zřejmě nastane až v roce 2017. Dále má Zen umět také rozšíření RdSeed, které by mělo produkovat entropii pro použití v softwarových generátorech náhodných čísel. Přibýt mají ještě Intelem nedávno zavedené instrukce SMAP (zamezení přístupu k režimu supervizora), XSAVEC, XSAVES a ClflushOpt, a dále ADX pro počty s libovolně přesnými celočíselnými hodnotami.

Instrukce XOP po pěti letech skončí

Podobně jako Bulldozer skoncoval s instrukcemi 3DNow!, které sice měly své uživatele, byly ale redundantní vzhledem k sérii rozšíření SSE, zmizí také ze Zenu některé instrukce specifické pro AMD a neexistující na čipech Intel. Asi nejvýznamnější obětí je rozšíření XOP, které přinesl Bulldozer. Vzhledem k minoritní roli si asi nenašlo mnoho uživatelů (v menší míře je ale uplatněno například v x264 – zejména permutační instrukce VPPERM). Podle určitých anekdotických informací z druhé ruky údajně také příliš zvyšovalo komplexitu FPU. AMD jej proto asi obětovalo v zájmu zmenšení jádra.

Zmizí údajně také rozšíření TBM (Trailing Bit Manipulation), které přinesl Piledriver a také rozšíření LWP (Light Weight Profiling), které měl poprvé Bulldozer. Podle mailu, který odpovědný vývojář zaslal, měla být dokonce zaříznuta i podpora nedestruktivního FMA4, zatímco částečně destruktivní FMA3 sdílené s Intelem by zůstalo. Tam ale asi došlo ke komunikační (pokud ne k programátorské) chybě, protože podle definice v samotném kódu má Zen nadále podporovat obě tyto mutace rozšíření FMA. Vzhledem k tomu, že se od FMA3 liší jen uložením finálního výsledku do registru, by ostatně nemělo valného smyslu FMA4 zrušit, neboť čip nijak výrazně nekomplikuje.

Suchá zahrada, jeden ze symbolů zenového budhismu

FMA = výkonné CPU?

Přítomnost FMA3/FMA4 v Zenu je zajímavá z jednoho důvodu. „Malá jádra“ Jaguar mají rozšíření AVX, neboť jej lze implementovat v podstatě se stejnými jednotkami, jako SSE4 rozkladem operací na dva 128bitové kroky. Rozšíření FMA do nich ale AMD na rozdíl od Bulldozeru nezačlenilo. Tyto operace jsou o něco vyšší komplexity, takže jejich přítomnost by mohla být určitou indicií, že má Zen blíže spíš k výkonným „velkým jádrům“ jako byl Bulldozer a K10 než k těmto úsporným, ale také pomalejším „malým jádrům“ typu Jaguar či Silvermont.

Seznam podporovaných instrukcí ovšem ještě nemusí být zcela definitivní. Finální specifikace CPU jednak ještě nemusí být uzavřeny – je možné, že některé zamýšlené funkce se nepodaří odladit a budou uměle vypnuty (stačí se podívat na dodatečné vypnutí TSX u Haswellů). Přehledy instrukcí poslané do Binutils ale také nemusí mít finální podobu, AMD do nich teoreticky může další změny zanést později. Nicméně prozatím asi tyto údaje můžeme brát za směrodatné.

Příchod prvních procesorů na bázi Zenu je očekáván v druhé polovině roku 2016. Na desktopu by údajně premiéra měla být prostřednictvím procesorů Summit Ridge, přímo zástupci firmy ale také potvrdili, že se tato architektura dostane rovněž do serverových CPU. I ta ale budou na trhu až příští rok.

Zdroje: AMD/Binutils (Mailing List), KitGuru