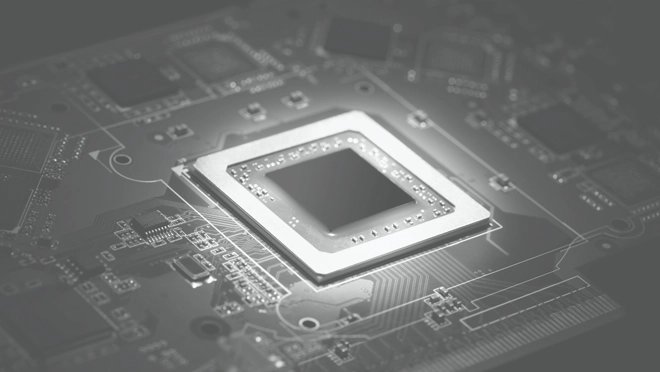

Od svého uvedení v roce 2011 byla APU, tedy procesory s integrovanou grafikou v podání AMD, jen řešením pro levnější počítače (a poté v jiné formě pro herní konzole). Firma se ale nikdy moc netajila, že by takovéto čipy jednou chtěla uplatnit i pro náročné výpočty, tedy v sektoru HPC a superpočítačích. Taková super-APU byla zatím jen ve stádiu konceptů pro superpočítače, plány s nimi ale AMD opět potvrdilo v nyní publikované studii. Ta předpokládá vizi architektury, která má dovolit stavět stroje s výkonem v řádu exaFLOPS (tedy tisícovek PFLOPS) a chce toho dosáhnout právě použitím heterogenních čipů, čili APU.

Jedná se spíše o jakousi studii proveditelnosti vykreslující, jaká by taková architektura měla být. Neberte tedy tyto informace tak, že AMD takové procesory chystá do výroby, to by byl asi chybný závěr. Pro dosažení výkonu v řádu EFLOPS bude muset mít jeden uzel v klastru se sto tisíci takovými členy prakticky dosažitelný (tedy nejen teoretický) výkon 10 TFLOPS a více, ovšem v dvojité přesnosti (v jednoduché by to tedy asi bylo 20 TFLOPS). Nedávno uvedená výpočetní grafika FirePro S9170 má v FP64 teoretický „průtok“ přes 2,6 TFLOPS, jenže v praxi s GPGPU v reálném kódu (měří se například Linpackem) plný výkon nedosáhnete.

Podle AMD bude alespoň z počátku nejvýhodnější, aby takto výkonné stroje používaly APU, tedy procesory, které budou integrovat jak řídící CPU, tak akcelerátor (GPU). Každý uzel pak totiž včetně chlazení nebude potřebovat tolik místa a důležité jsou zde také ohledy na spotřebu, která je u superpočítačů v řádu megawattů (tyto stroje tedy mohou spotřebovávat ne nevýznamný zlomek výkonu jednoho jaderného reaktoru) a je třeba ji co možná krotit. Tomu pomůže například flexibilní rozdělení TDP mezi jednotky GPU a CPU. Integrace má ale i výkonnostní výhody z hlediska latence a přesunů dat – heterogenní čip unifikovaný stylem HSA by měl být při využití své teoretické výpočetní síly efektivnější než nezávislé GPU připojené k CPU části externě.

Exascale APU bude mít integrovanou 3D paměť a nevolatilní RAM

Na obrázku ze studie můžete vidět konceptuální schéma takového uzlu. Procesor integruje GPU jednotky s velkým počtem jader CPU, nemusel by ale asi být monolitickým čipem – ostatně AMD má zdá se od architektury Zen v plánu kombinovat více čipů, jako dříve u Opteronů Magny Cours a Interlagos. Ve studii se zdá se nepočítá napevno s architekturou x86 (což by byl u AMD Zen či jeho pozdější derivát), použité mohou být například i jádra ARM. GPU komponenta by mohla být v takovém vícečipovém modulu také osazena samostatně, což by dovolilo použít masově vyráběné čipy z herních grafik – to je důležité, neboť trh HPC není velký a vyvíjet speciální čip jen pro něj je proto velmi drahé.

AMD: Koncepce APU pro superpočítače s výkonem v řádu EFLOPS (Zdroj: HPCwire)

Zvažovaný procesor (AMD mu zde říká EHP – „exascale heterogeneous processor“) by měl zároveň integrovanou rychlou paměť HBM nebo podobného typu v roli první úrovně hierarchie RAM. Zajímavé je, že také druhá úroveň mimo čip nebude v takovýchto budoucích APU konvenční – podle AMD by měla být použita místo prosté DRAM (DDR4) rovnou nějaké forma nových nevolatilních pamětí. Ty by měly menší spotřebu a větší kapacitu umožňující řešení náročnějších problémů, přičemž jejich menší výkon by doháněla rychlá DRAM v procesoru. Volitelně by pak každý uzel mohl mít i konvenčnější úložiště (SSD). Tento systém by pak doplnila ještě propojovací logika či síťová rozhraní pro komunikaci uzlů v celém klastru.

Asi je potřeba ještě jednou vypíchnout, že popsané představy o budoucím „exascale“ APU jsou spíše koncepční či přímo spekulativní. Nikde není psáno, že už na takovém čipu AMD pracuje nebo že ho hodlá komerčně vyrábět. Z toho důvodu je také třeba ošidné počítat jádra CPU zobrazené na slajdu a vyvozovat z toho, že tento čip bude 32jádrový. V referátu samotném zdá se žádné takové podrobnosti nejsou a pokud by byly, šlo by asi opět jen o koncepční úvahy a rozhodně ne o cosi jako roadmapu nebo předestření budoucího produktu.

AMD uvádí, že serverová APU, jejichž vývoj by eventuálně směřoval takovýmto směrem, již ve vývoji má. Mohlo by snad jít o šestnáctijádro na bázi Zenu, o němž před časem psal web Fudzilla. Tyto první vlaštovky superpočítačových APU by snad měly jít na trh už v letech 2016 až 2017, nejedná se ale o „EHP“, o nichž byla tato „exaflopsová“ studia. Ty jsou zřejmě jen v koncepčním stádiu a jejich eventuální vznik asi bude podmíněn až tím, zda o ně počítačový průmysl vůbec bude mít zájem.

Údajné schéma dalšího připravovaného APU pro sektor HPC se objevilo už letos na jaře (Zdroj: Fudzilla)

Zdroj: HPC Wire