Procesory rodiny Tile je asi třeba trochu přiblížit. Jedná se o mnohajádrové čipy postavené na vlastní 64bitové architektuře typu VLIW. Firma Tilera měla za cíl vytvořit procesory s vysokým množstvím jader propojených na čipu do síťové topologie, kteoru nazývá iMesh. Tilera byla v oboru mnohajader průkopníkem, a i proto se zřejmě rozhodla vyvinout vlastní architekturu. Početná jádra totiž musela být co nejjednodušší, nejúspornější a nejmenší. Notně očesaná instrukční sada a architektura není až takovým hendikepem, jelikož jsou tyto čipy určené zejména pro síťový hardware, přepínače a servery.

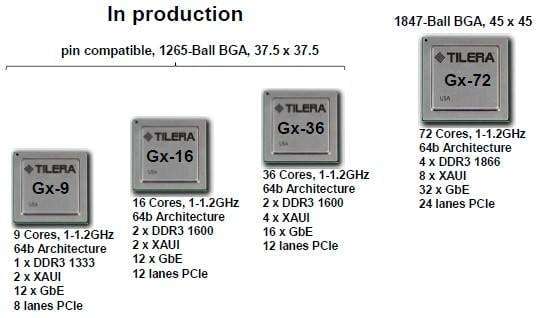

Procesory Tile-Gx, o nichž je momentálně řeč, jsou (pokud dobře počítám) již třetí generací této architektury. Ve firmě časem zřejmě zjistili, že zcela minimalistické jádro přece jen neuspěje, neboť v některých úlohách (obrazně řečeno) ani velký počet lopat nestačí na bagr. Tile-Gx tak již na rozdíl od předchůdců (Tile64 a TilePro64) disponuje FPU a dokonce podporuje i instrukce SIMD. Daní za vyšší složitost byl ale právě počet jader. Zatímco předchozí generace jich měly 64, Tile-Gx začalo na 16 a 36 (jak vidíte, použito je čtvercové symetrické uspořádání).

Již někdy v roce 2009 Tilera slibovala, že opět uvede i 64jádro a navíc i variantu s rovnou stovkou jader. Jenže ze slibů nakonec nic nebylo – tedy až do této doby. Tilera včera oznámila, že k 16ti a 36jádrovou verzi nakonec přibude model se 72 jádry; jeho vzorky mají prý už být k dispozici. Modely s „pravidlenými“ konfiguracemi 8 × 8 a 10 × 10 jader jsou tedy podle všeho zrušeny – dle serveru SemiAccurate je prostě nešlo optimálně navrhnout (a vyrobit). Na čipu tedy bude jen devět řad po osmi jádrech.

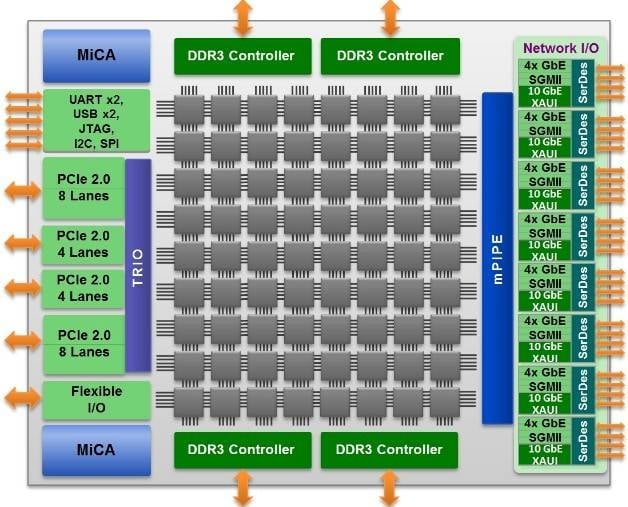

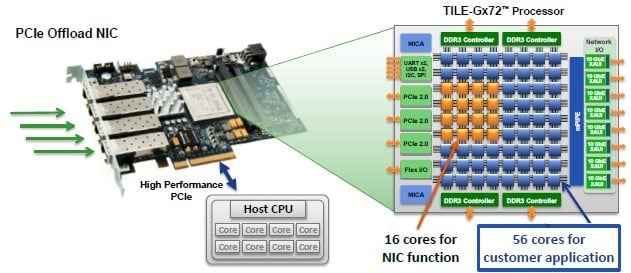

Tile-Gx72 (Tilera někde používá označení Tile-Gx8072) se má vyrábět 40nm procesem u TSMC a taktován má být na 1 GHz (v budoucnu snad 1,2 GHz), a to při TDP zhruba 60 W. Na čipu bude mít vedle matrice jader čtyřkanálový řadič DDR3 (do 1866 MHz), osm 10Gb rozhraní Ethernet (která lze přeskupit na 32 gigabitových) a celkem 24 linek PCI Express v šesti portech. Ve všech těchto parametrech tak vlastně jde o zdvojenou kopii Tile-Gx36 (konfigurace čipů Tile-Gx vidíte na obrázku). Na čipu má být přítomno 18 MB L3 cache (každé jádro má 256KB L2 a L1 cache tvoří 32+32 KB). Mimo to jsou přítomny také akcelerátory pro analýzu paketů (mPIPE) a šifrování (MiCA).

I vzhledem k zdvojnásobení schopností vstupu/výstupu je logické, že čipy nebudou zpětně kompatibilní. Jejich pouzdro typu BGA bude mít 1847 kontaktů oproti předchozím verzím (36jádro, 16jádro, a také jednodušší 9jádrový model), které si vystačí s 1265 kontakty. Rozměr pouzdra je 45 × 45 mm, plochu čipu (či počet tranzistorů) jsme se bohužel nedozvěděli.

Jak to bude s dostupností, bych raději sám nepředjímal. 36jádrová verze ohlášená v roce 2009 se na trh prý dostala až loni, takže nelze vyloučit, že od včerejšího oficiálního ohlášení Tile-Gx72 také uplyne dlouhá doba, než se ony čipy objeví v serverech. I přes svou exotičnost si však prý CPU Tilera nevedou zle, údajně se mají nacházet mimojiné v některých MikroTicích a tchajvanská Quanta na nich v malých sériích staví servery. Vedle síťové infrastruktury by je Tilera ráda viděla i v úlohách jako je paralelní zpracovávání videa.

Zdroje: Tilera, SemiAccurate, The Register