Není to tak dlouho, co jsme tu psali o tom, jak firmy Toshiba a WD/SanDisk (tyto společnosti mají společný podnik) uvádějí 96vrstvé čipy 3D NAND. Vrstvená neboli 3D NAND se ale podle všeho nadále vyvíjí rychlým tempem a tak už teď přichází zprávy o další generaci. Ta přinese rovnou 128 vrstev a mohla by zřejmě zlevnit díky menší ploše. Hlavně ale zdá se chystá zlepšení, která by se měla projevit o dost lepším výkonem.

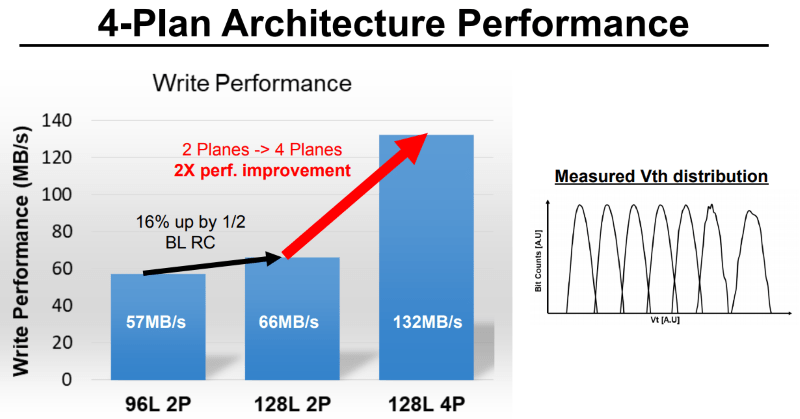

Čtyři oddíly pro dvakrát rychlejší zápis

128vrstvé čipy budou představovat pátou generaci 3D technologie NAND, Toshiba jim proto bude říkat „BiCS-5“ (BiCS znamená Bit Cost Savings). Kapacita těchto čipů má být 512 Gb (64 GB) na jeden křemík – nebo alespoň z počátku, později asi může firma vyvinout i další velikosti. Tento první 512Gb čip bude zajímavý ještě tím, že zůstane na zápisu TLC a Toshiba/WD se s ním nebudou tlačit do záznamu QLC se zhoršenou životností a výkonem.

Výkon by naopak mohl být lepší proti předchozí TLC 3D NAND. V návrhu totiž byly učiněné změny za tímto účelem. BiCS-5 bude používat rozdělení čipu na čtyři samostatné oddíly (planes), zatímco 96vrstvá generace BiCS-4 měla jen dvě takové sekce. Tyto oddíly přitom umožňují separátní přístup, takže ve výsledku bude čip BiCS-5 teoreticky moci najednou vykonávat dvakrát víc přístupů paralelně a měl by se tím o dost zlepšit výkon. Tyto čipy by díky tomu měly mít dvakrát lepší rychlost zápisu na jeden kanál, 132 MB/s místo předchozích 66 MB/s. SSD se stejným počtem čipů by tak mohlo vyvinout podstatně lepší reálnou rychlost zápisu v sekvenčním přístupu.

Circuit under Array (aneb „4D“)

Více separátních oddílů je pro výkon velmi dobře, ale je důvod, proč jich předtím bylo méně. Tato paralelizace stojí v křemíku nějakou plochu a čip prodražuje. Ubere tedy i něco z výhod toho, že má čip více vrstev a tím menší plochu. WD a Toshiba ovšem nárůst plochy o něco vykompenzovala jinde. Tyto čipy jako první použijí technologii CuA, neboli Circuitry under Array.

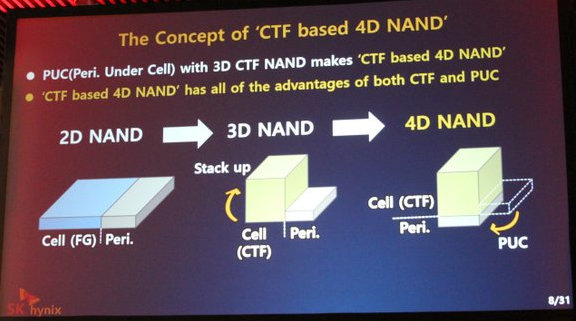

Všechny čipy NAND potřebují kromě samotných záznamových buněk také určitou obslužnou logiku okolo. A to okolo je zde doslova, protože logika bývá po okrajích čipů. Zvyšuje tím jejich plochu a snižuje množství čipů, které se vejdou na jeden wafer. Navíc zatímco buňky jsou ukládány do vrstev a tím se jejich plocha může zmenšovat, logika se takto nezhustí. Řešení je ale uložit tyto bloky do samostatné vrstvy, která bude v základech čipu vespod, schovaná pod buňkami. A to je přesně to, co CuA dělá. Díky CuA návrhu je prý plocha asi o 15 % nižší než se starou koncepcí. Celkově má čip být o 23 % menší než 512Gb TLC čip 96vrstvé generace.

Slajd Hynixu: technologie Circuit under Array (či Periphery under Cell) přenáší obslužné logické obvody čipu pod vrstvy NAND (Zdroj: Tom's Hardware)

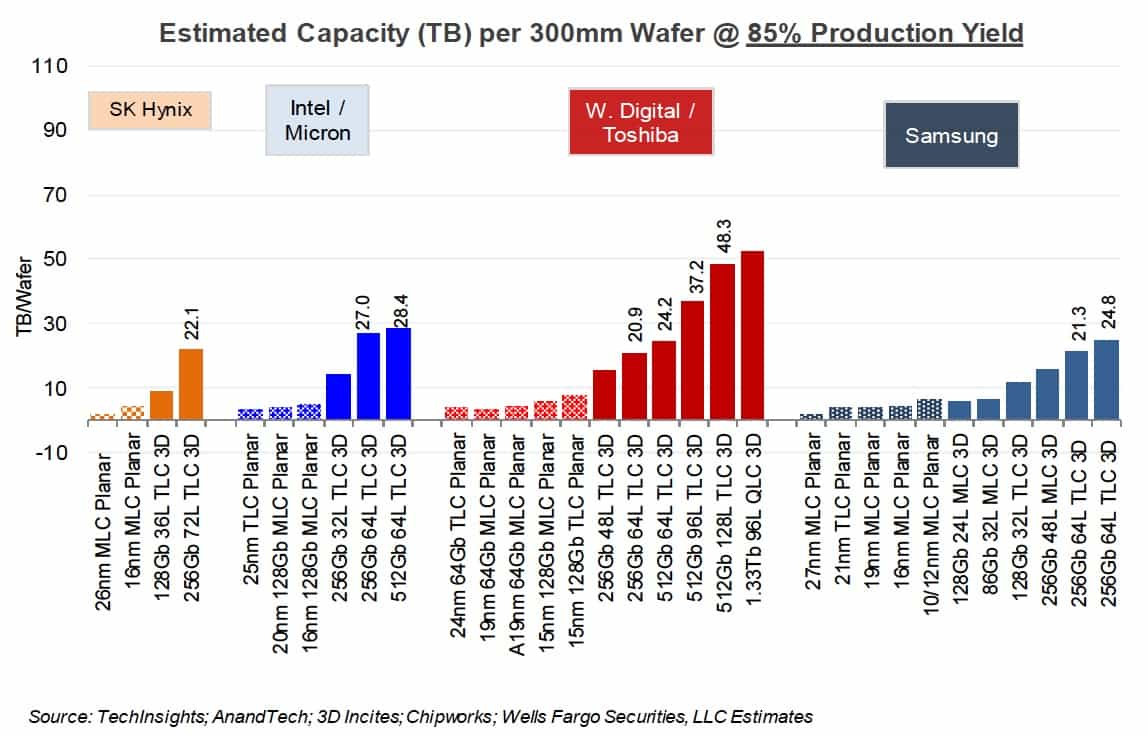

Slajd Hynixu: technologie Circuit under Array (či Periphery under Cell) přenáší obslužné logické obvody čipu pod vrstvy NAND (Zdroj: Tom's Hardware)Tuto technologii již před časem oznámil Hynix pod označením „4D NAND“. Toshiba a WD tedy půjdou stejnou cestou. Výhledově by ovšem asi CuA měli používat všichni výrobci a jde o známou evoluční cestu, takže nelze úplně říct, že by se tu opisovalo. Každopádně by technologie CuA měla zmenšit náklady na výrobu určité kapacity NAND, protože se na wafer vejde celkově víc gigabajtů. A tím pádem by měla umožnit snížení cen paměti NAND a úložišť.

Odhad kapacity v gigabajtech, kterou je možné vyrobit z jednoho waferu s různými generacemi 3D NAND (Zdroj: EE Times)

Odhad kapacity v gigabajtech, kterou je možné vyrobit z jednoho waferu s různými generacemi 3D NAND (Zdroj: EE Times)V provozu až příští rok

Tento čip byl letos prezentován na ISSCC, což je zdroj informací k němu – pochlubil se s ním Western Digital. Zatím je ale ještě relativně daleko od nasazení, momentálně se teprve rozjíždí prodej zařízení založených na 96vrstvé předchozí generaci. Tato 128vrstvá novinka se tak údajně má objevit až v závěru roku 2020, s větším rozšířením produkce až po jeho konci, v roce 2021.