Minulý měsíc jsme tu psali o novém x86 procesoru navrženém firmou Centaur Technology, která vám možná je neznámá, ale stála za všemi x86 CPU VIA a Zhaoxin a tím také jedinou konkurencí, kterou v posledních 15 letech měly firmy Intel a AMD. Zjistili jsme tehdy, že má jít o osmijádro na 16nm procesu TSMC s novou architekturou CPU a také s integrovanou jednotkou pro akceleraci neuronových sítí („AI“ výpočtů). Už podle uniklých benchmarků či toho, že je podporováno AVX-512, to vypadalo, že samotná jádra CPU by také mohla být zajímavá. Nyní se dostaly ven další informace, které jejich architekturu popisují podrobně a skutečně: nové jádro pro VIA/Zhaoxin se v mnohém dá srovnávat s Haswellem, Skylake či Zenem 2 od AMD, byť v jiných ohledech se zase liší.

Třetí dodavatel x86 procesorů má konečně něco nového

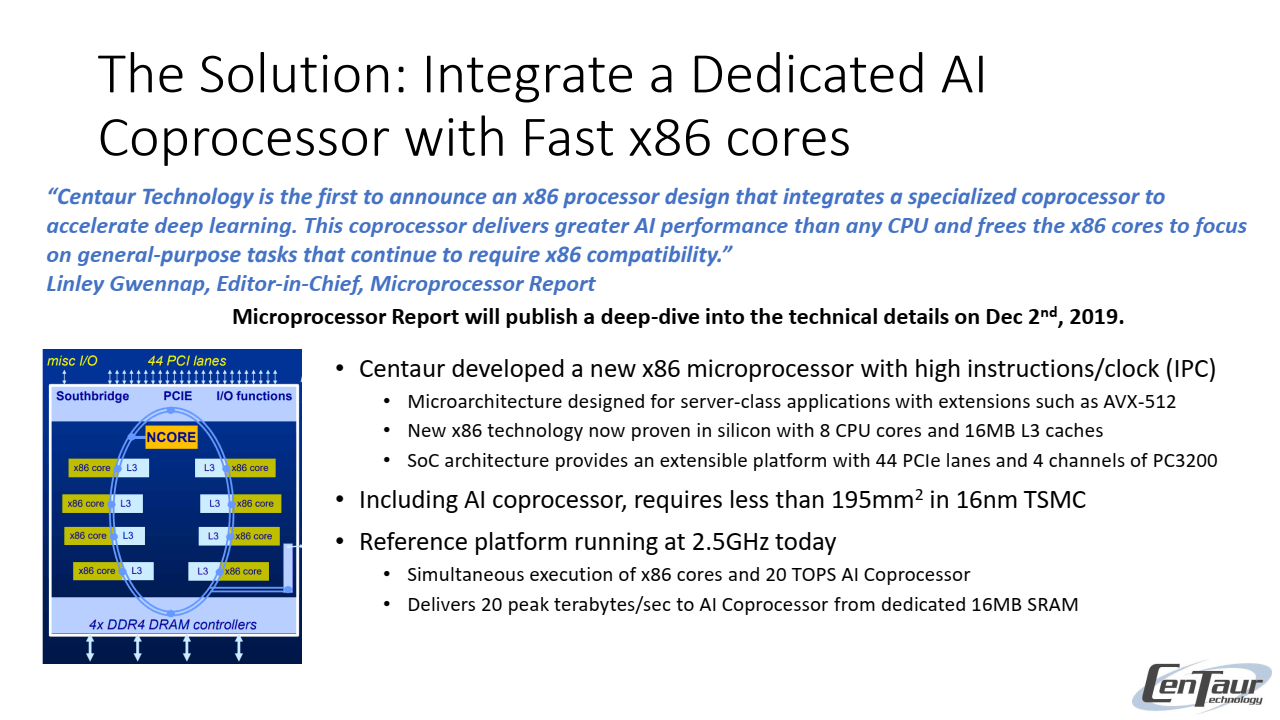

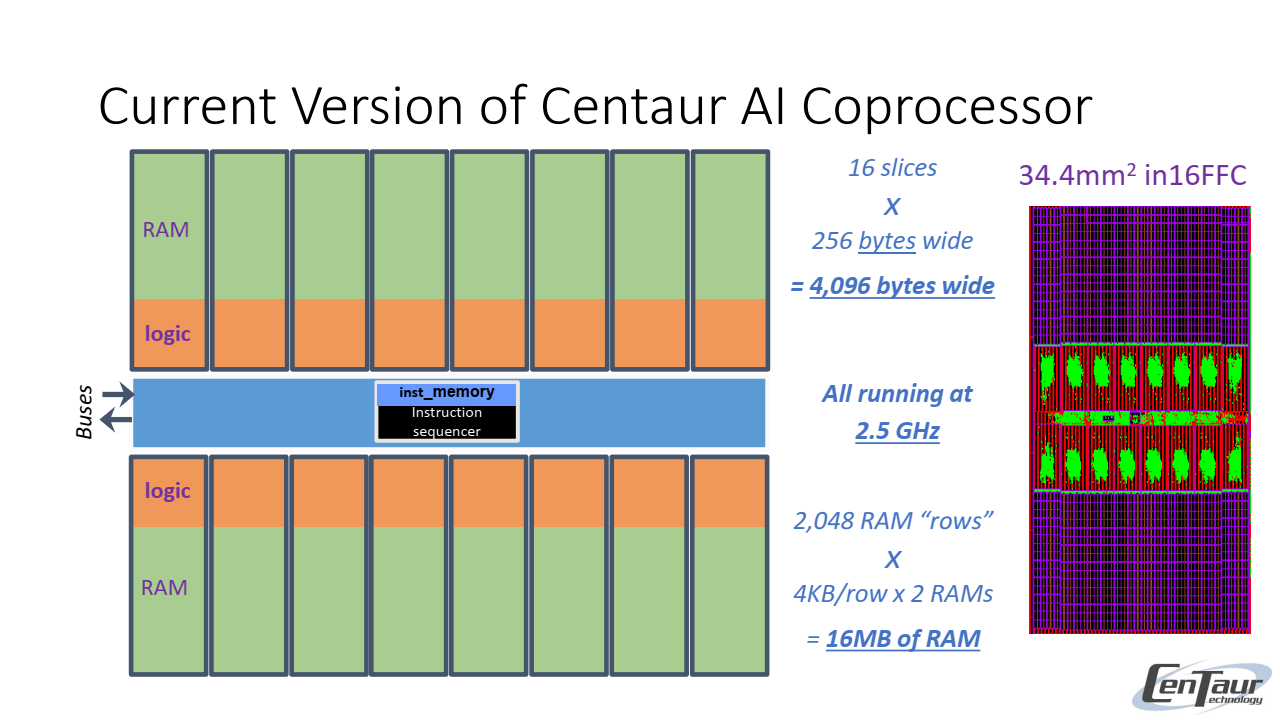

Pod jakým označením a jakou značkou (tedy zda VIA, nebo Zhaoxin) se toto CPU dostane na trh, není ještě jasné. Centaur o návrhu tohoto čipu mluví jako o čipu s kódovým označením „CHA“ a jeho jádra měla interní kódové označení „CNS“. Podle slajdů a zveřejněných informací bude procesor Centaur CHA obsahovat osm jader CNS a na 16nm procesu TSMC dosahuje plochu 194 mm². Pro srovnání, to je něco málo přes 90 % také osmijádrového Zenu od AMD, čipu Zeppelin použitého ve 14nm Ryzenech a Epycích. Centaur se pochlubil, že již má funkční referenční platformu, v níž toto cpu běží na 2,5 GHz, což ale ještě nemusí být frekvence finální.

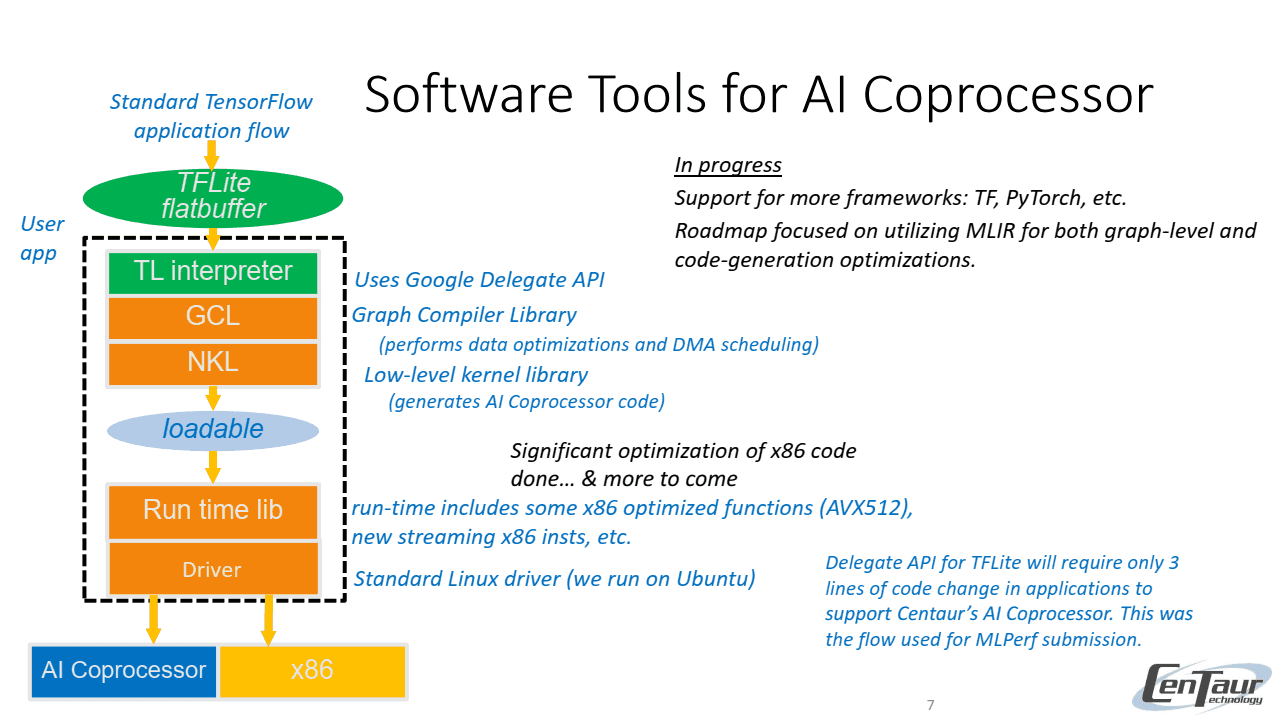

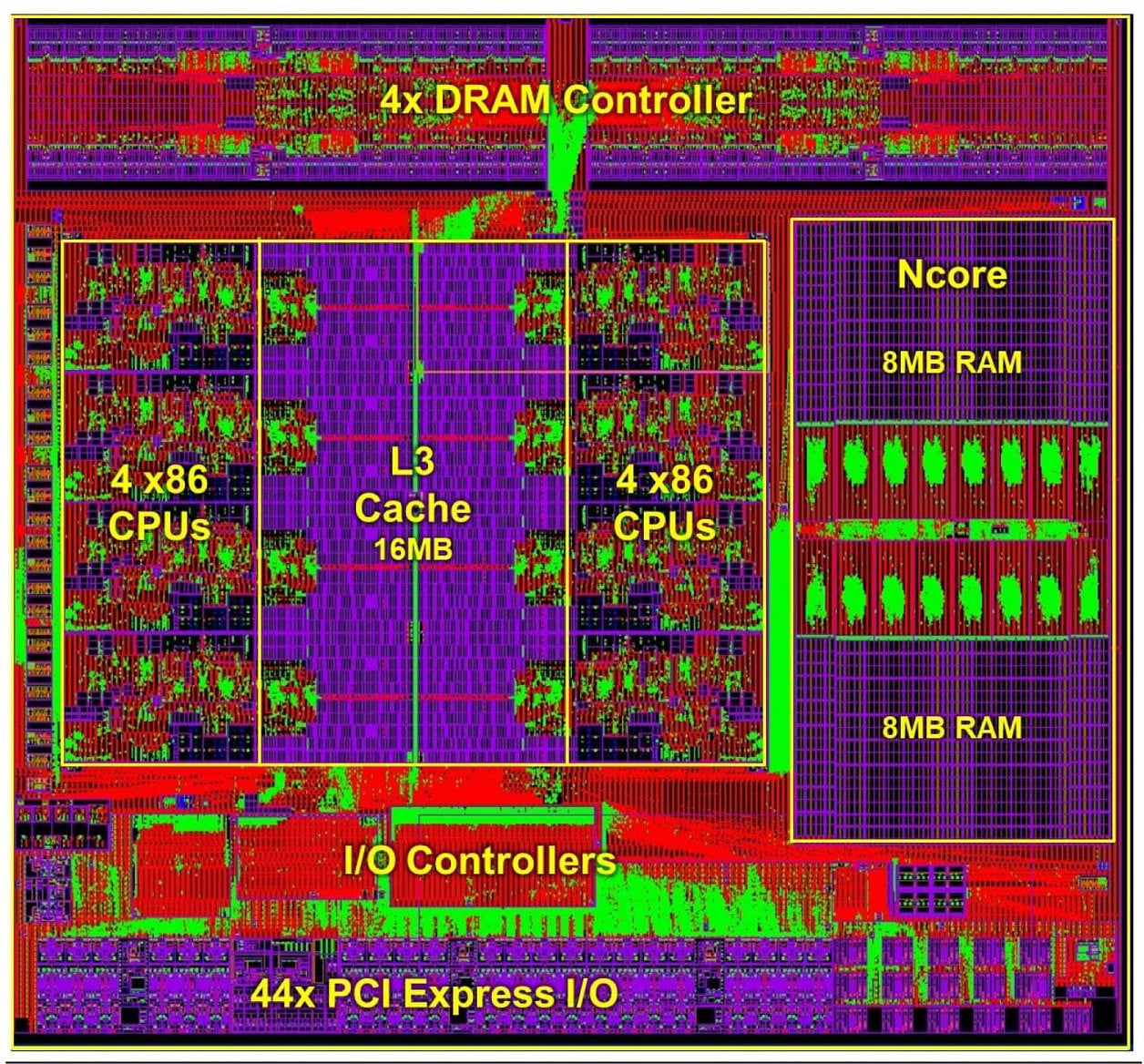

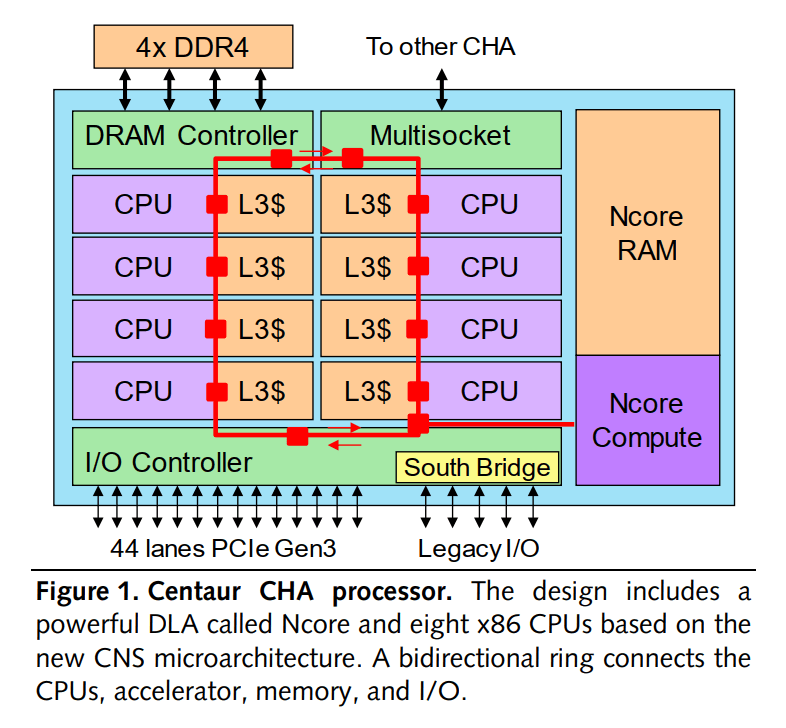

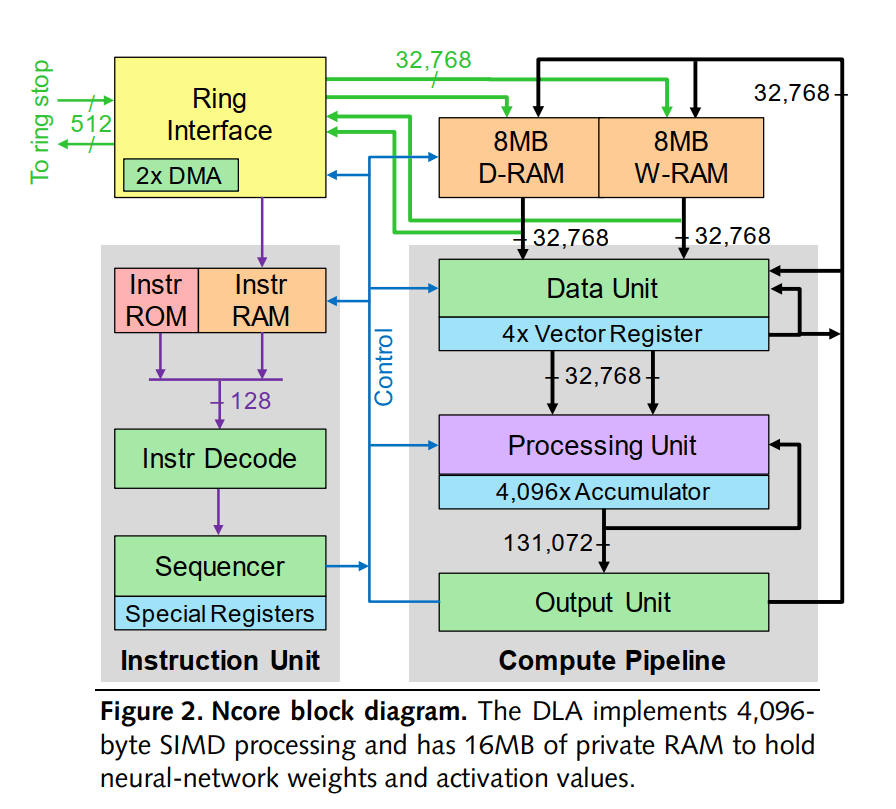

Procesor bude mít jádra propojená prstencovou sběrnicí, každé z osmi jader bude spolu s přidruženým 2MB blokem L3 cache (takže celkem 16 MB L3) jednou zastávkou, další bude představovat integrovaný řadič PCI Expressu (poskytuje 44 linek PCIe 3.0) a dalšího IO („Southbridge“) a paměťový řadič, jenž je čtyřkanálový s podporou DDR4-3200 a ECC. A separátním klientem přímo na tomto ringbusu bude také speciální AI koprocesor NCore, kterému se zde nebudeme už znovu věnovat. Sběrnice má šířku 512 bitů a je obousměrná (jde tedy vlastně o dva 512bitové ringbusy). Pro srovnání, u Haswellu či Skylake je šířka jenom 256 bitů.

Mimochodem, ve schématu chybí integrovaná grafika, takže tento čip asi nebude určený pro běžná PC. Podle všeho je jeho hlavním cílem server, nicméně sekundárně by mohl sloužit v desktopu. Tato architektura je hodně podobná současným klientským (a starším serverovým) procesorům Intel a konektivita PCIe a čtyřkanálový řadič pamětí zase hodně odpovídají platformě LGA 2011.

Na fotkách zveřejněných firmou Centaur, které mají zachycovat práci ve firmě, jsou vidět inženýři pracující s procesory a deskami se socketem LGA 2011 (přesněji LGA 2011-3, jenž používají Haswelly-E/Broadwelly-E s pamětmi DDR4). Je teoreticky možné, že Centaur zrecykluje fyzickou podobu socketu či jeho komponenty pro zjednodušení výroby, i když nevím, zda to třeba dovolují patenty (teoreticky by se tyto komponenty mohly používat jen pro prototypy).

Fotky firmy CentaurTech zachycující práci na prototypovém hardwaru. Desky a CPU mají (provizorně?) patici podobnou LGA 2011-3 od Intelu

Fotky firmy CentaurTech zachycující práci na prototypovém hardwaru. Desky a CPU mají (provizorně?) patici podobnou LGA 2011-3 od InteluJádro Centaur CHA podrobně

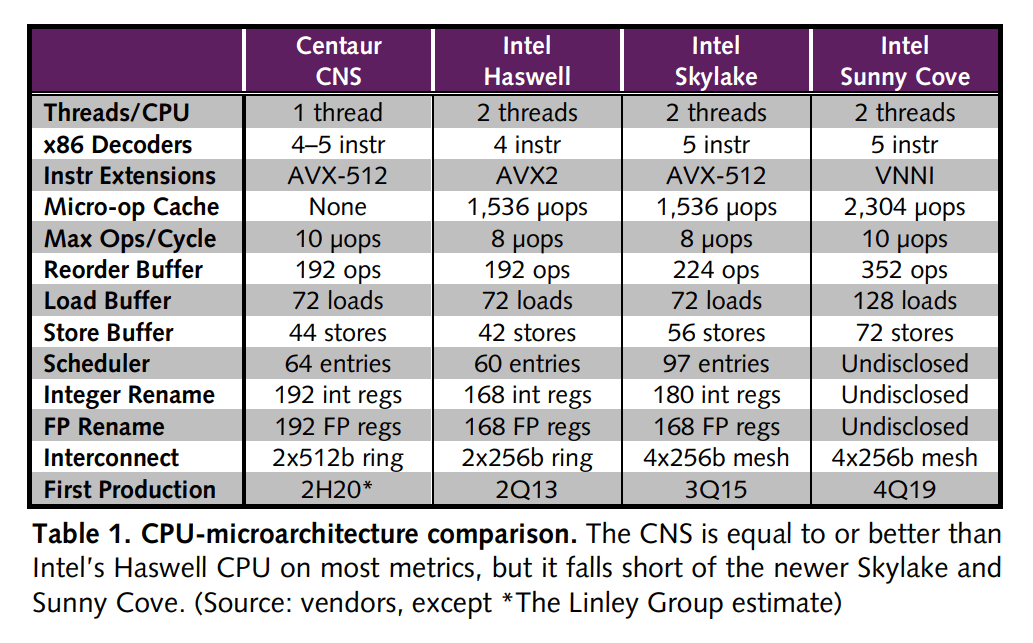

Centaur na svém webu uveřejnil článek o čipu CHA a architektuře CNS z Linley Group Microprocessor Report (na což jako obvykle upozornil Tralalák), takže se můžeme podívat na detaily jádra, které leccos naznačí i o výkonu. Jádro CNS je podle firmy zaměřeno na vysoké IPC, frontend počítá se zpracováváním čtyř instrukcí za jeden cyklus, špičkově může do výpočetních jednotek backendu poslat až 10 microOPů. Celkově by mělo jít o velký skok proti předchozí architektuře Centauru/VIA/Zhaoxin, která víceméně vycházela stále z architektury Nano/Isaiah (z roku 2008).

Jádro CNS má frontend, kde fáze fetch v každém cyklu může dodat až 32B kódu z L1 cache. Tento blok prochází fází pre-decode, v níž jsou nalezeny začátky jednotlivých instrukcí (jelikož u x86 nemají konstantní délku). Poté již jdou takto označené/vypreparované instrukce k dekódování. Zatímco předchozí architektura měla tři dekodéry, CNS již obsahuje čtyři, jako procesory Intel od Conroe až po Haswell nebo Zen/Zen 2. Dekodéry dokáží zpracovat čtyři instrukce, v některých případech pět, pokud se nějaké dvě instrukce povede sfúzovat. Do dalšího zpracování z dekodérů může jít až 6 microOPů za cyklus (je jich víc než je propustnost x86 instrukcí, protože některé mohou být dekódované na více microOPů).

Bez microOP cache

Dekódování se ale týká ještě jedna zásadní odlišnost proti současným jádrům Intelu a AMD. Ta od Sandy Bridge (a AMD od Zenu) používají tzv. microOP cache. V ní jsou cachovány již dekódované instrukce (má kapacitu 1500 i více položek), které například ve smyčkách může CPU brát přímo z této mezipaměti a nemusí je znovu hnát přes fetch a dekodéry. Toto snižuje spotřebu, ale také zvyšuje výkon, typicky většina instrukcí (třeba až 80 %) může jít z microOP cache místo ze standardní pipeline, například AMD tuto funkci označovalo za jednu z nejdůležitějcíh novinek architektury Zen. Centaur však microOP cache alespoň zatím neimplementoval, tento zlepšovák v jádru CNS není a představuje to pravděpodobně jeden z deficitů, které ho mohou proti konkurenčním jádrům poněkud omezovat v rozletu.

Naopak docela srovnatelná je architektura Centauru v hloubce out-of-order front, které by měly umožňovat celkem efektivní vytěžení potenciálního IPC z kódu. Reorder buffer, tedy okno, které procesor vidí a v jehož rámci může přehazovat operace pro maximální využití vykonávacích jednotek, má 192 položek, jako Haswell nebo AMD Zen. Fronta unifikovaného scheduleru má 64 položek (Haswell: 60, Skylake: 97). Zajímavé je přejmenování registrů. Fyzický soubor má u CNS ještě více použitelných registrů než Skylake: 192 klasických a 192 pro FPU/SIMD (u Skylake je to 180/168).

Čtyři ALU, tři jednotky AGU, tři pipeline v FPU

V samotném výpočetním backendu má jádro CNS už šířku 10 „portů“ či „pipeline“, do nichž lze teoreticky ze scheduleru nasypat najednou až deset microOPů, pokud by měly přesně správnou skladbu. Tato šířka je stejná jako u Zenu, ovšem skladba jednotek je mírně jiná. Jádro obsahuje čtyři celočíselné ALU, z nichž násobení podporují dvě, druhé dvě mají místo toho jednotky pro manipulaci s bity (základní operace a sčítání budou umět všechny). ALU také dokáží zpracovat dvě větvení za cyklus.

Ale Centaur se rozhodl jinak než AMD u Zenu dimenzovat FPU a AGU, čili load/store jetnotky. Zatímco Zen měl jen dvě LSU/AGU, jádro CNS má tři load/store jednotky či porty a dokáže provést dvě čtení z paměti (cache) o šířce 256 bitů, nebo jeden zápis o šířce 256 bitů (nebo dva spojené). AMD přidalo třetí AG/LSU až v Zenu 2. Fronta pro čtení pojme 72 položek, fronta pro zápisy 44. Toto je prakticky stejné jako u Haswellu (72/42) nebo Zenu 1 (72/44).

Naopak na FPU, respektive jednotku SIMD klade Centaur zřejmě menší důraz než AMD, protože má místo čtyř pipeline jenom tři. Ovšem jako u Zenu 2 jsou už tyto jednotky 256bitové a umí provádět instrukce AVX/AVX2 v jednom cyklu. Dvě z pipeline FPU budou podporovat floating-point operace FMA, třetí bude mít FP děličku a jednotku akcelerující (de)šifrování AES. Všechny tři pipeline budou zvládat celočíselné instrukce AVX2. Latence FMA je pět cyklů, latence sčítání nebo násobení jsou tři cykly. V SIMD kódu tak může nastat dramatické zlepšení, což potěší mimo jiné multimediální a HPC aplikace.

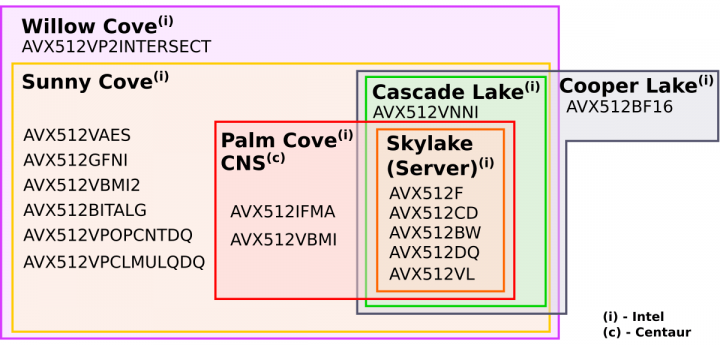

Podpora AVX-512. Poprvé mimo Intel

Navíc bude tato jednotka už umět AVX-512, což zatím AMD nemá a Intel podporuje jen na serverových jádrech Skylake-X/SP a novějších a Ice Lake (architektura Sunny Cove). 512bitové operace AVX-512 se ovšem budou zpracovávat s polovičním výkonem, protože se pro ně budou používat dva microOPy (dva průchody jednotkou). Nicméně kompatibilní CPU bude, uvidíme, zda někde třeba nedosáhne zlepšení výkonu díky některým zlepšením efektivity, které AVX-512 umožňuje. Je třeba upozornit, že i velká řada levnějších Xeonů má poloviční výkon AVX-512. Pokud AMD nedodá podporu pro AVX-512 v Zenu 3, tak možná Centaur/VIA/Zhaoxin budou první mimo Intel, kdo AVX-512 bude podporovat.

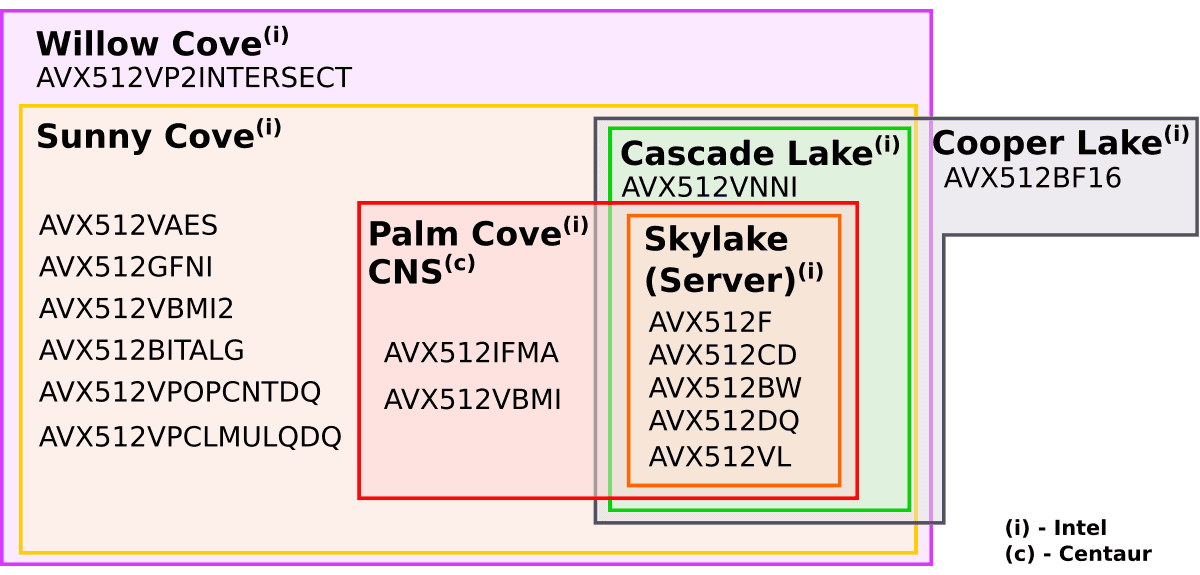

Mimochodem: AVX-512 má úplnou džungli subsetů, z nichž jednotlivé procesory Intelu podporují různé podmnožiny. A ne nutně tak, že by novější jádro vždy umělo vše, co ta předchozí. Podpora AVX-512 je tedy poněkud složitější otázka než ano/ne. Dle webu Wikichip by Centaur CNS údajně měl umět ty subsety, co jádro „Palm Cove“ v 10nm procesoru Cannon Lake (de facto zrušeném). Měly by to být subsety F, CD, BW, DQ, VL, IFMA a VBMI. Má tedy víc rozšíření než Skylake-X/SP a některá, které nemá Cascade Lake-X/SP.

Cache

Jádro má 32KB instrukční L1 cache a 32KB datovou L1 cache s osmicestnými asociativitami. Jak už bylo řečeno u LSU pipeline, z datové L1 cache lze provést dvě 256bitová (32bajtová) čtení nebo jeden 256bitový zápis. Z L2 cache do L1 lze přenášet 64 bajtů za cyklus. L2 cache má 256 KB na jedno jádro, jako jádra Intelu od Nehalemu po Skylake (ovšem ne jeho serverovou verzi). Celý procesor pak má 2 MB L3 cache na každé jádro, což opět odpovídá všem moderním ringbusovým architekturám Intelu.

Hloubka pipeline: 20 až 22 stupňů

Podle zprávy Linley Group má jádro CNS celkovou pipeline hlubokou 20 stupňů pro běžné celočíselné/logické operace, ovšem operace jdoucí přes FPU mají pipeline o 22 stupních. To je relativně hlubší pipeline, nicméně dnes celkem standardní pro x86 procesory (ne tak už jádra ARM). Pro přístup ke cache je například použito celkem pět stupňů pipeline, což má prý za cíl zvýšit dosažitelné frekvence (zdá se, že srovna v těch má Centaur největší bottleneck). Přesto ale takty budou o dost nižší, než co dosahují jádra AMD, nemluvě o Intelu. Zřejmě by to mohlo být způsobeno tím, že Centaur investuje o dost méně času a prostředků (jeho vývojový tým je relativně malý) do vyladění fyzického designu a nemůže kvůli tomu vyhnat jádro na tak vysoké frekvence. Momentálně vzorky běží na 2,5 GHz při použití 16nm procesu TSMC.

IPC blízko moderním x86 procesorům, nižší takty?

Design jádra vypadá slibně, pokud ho nebudou trápit nějaké neefektivity nebo vnitřní problémy, mohl by tedy skutečně dosahovat hodně slušného IPC, i když za Zenem a Skylake nejspíš zaostane a Intel Sunny Cove by už mělo být v IPC o hodně napřed. Architektura je ostatně kladena spíš jako analogie Haswellu (v leckterém parametru je před ním, ale uvidíme, nemusí mít nutně vyšší IPC). Deficitem je jak už bylo řečeno chybějící microOP cache, ale pro celkový výkon budou hrát roli i ony nižší takty. Ovšem pokud půjde o serverová CPU, nemusí to vadit tolik, protože Xeony a Epycy mají typicky o dost nižší frekvence, než desktopová Core a Ryzeny. Procesor bude asi soutěžit zejména s jejich levnějšími modely.

Tip: Haswell je zde. Inovace a architektura nové generace procesorů Intel (2013)

Tip: Co dělá Skylake Skylakem. Aneb architektura nových procesorů Intel (2015)

Tip: Architektura jádra Zen podrobně: hledání rovnováhy a přiblížení Intelu (2017)

Tip: CPU jádro Zen 2 detailně: nová architektura AMD přináší hlubší změny, než se čekalo (2019)

Jako konkurence Intelu a AMD by ale jádro CNS mělo fungovat a umožnit snad Centauru širší uplatnění na trhu, než dosud. Důležité je také to, že vývoj bude pokračovat a v roadmapě Centauru jsou další generace se zlepšeními.

Vyjde Centaur CHA/CNS jako procesor Zhaoxin?

Podle Linley Group by zřejmě tento procesor – neboť nejde jen o papírový návrh ve stylu jader ARM, ale přímo i již implementovaný 16nm čip – mohl snad přijít na trh někdy v druhé polovině roku 2020, ovšem jde asi hlavně o očekávání (dlužno říct, že u Zhaoxinu/VIA byl často problém s tím, že na reálné uvedení se předlouho čekalo). Co ale zatím není vůbec jasné, pod jakou značkou vlastně. Doposud dílo Centauru vždy uvedla na trh tchajwanská VIA nebo v nedávnější době pevninsko/komunisticko-čínský Zhaoxin.

Nové čipy vypouštěl v poslední době jen Zhaoxin, ne VIA. Ten ale zase v roadmapě zdá se nemá nic, co by čipu CHA odpovídalo. Procesory Zhaoxin KX-7000 – které jsme doteď asi mylně považovali za identitu tohoto nového procesoru CHA od Centauru – mají prý být již 7nm a podporovat PCIe 4.0 a DDR5, takže nemůže jí to 16nm čip CHA, ale buď o další generaci, nebo Zhaoxin tentokrát převezme od Centauru jen IP, a ne celý návrh čipu. Zhaoxin počítá také se 16nm procesory KH-40000 pro servery, ale ty zase mají mít 32 jader. Opět by tedy muselo jít o nějakou nepřímou adaptaci technologie z Centaur CHA, ne o ten samý čip.

Roadmapa procesorů Zhaoxin. Předstvený 16nm Centaur CHA s osmi jádry do ní moc nezapadá (Zdroj: Tralalák)

Roadmapa procesorů Zhaoxin. Předstvený 16nm Centaur CHA s osmi jádry do ní moc nezapadá (Zdroj: Tralalák)Centaur pravděpodobně nemůže procesor „CHA“ vydat přímo sám a prodával jej pod vlastní značkou, mimo firmu VIA nebo čínské partnery. Pokud ho k tomu opravňují smlouvy a patenty (licenci na architekturu x86 by totiž neměla držet Centaur Technology, ale VIA), pak by se na trhu nečekaně objevila nová značka, což by bylo docela pozoruhodné, byť by pod ní ve skutečnosti byl již ostřílený tvůrce.

...nebo návrat VIA?

Samotná VIA v poslední době žádný nový x86 procesor neuvedla, až to skoro svádí k tomu, ji z tohoto trhu odepsat. Skutečně to trochu vypadalo, že založením Zhaoxinu se těchto snah vzdala. Ale Linley ve zprávě zdá se počítá s tím, že návrh CHA s jádry CNS bude komercializovat právě ona, byť ta oficiálně nic neoznámila. Dávalo by to i smysl, jelikož jak už bylo řečeno drží licenci na x86 a Centaur i vlastní. Pravda, teoreticky je možné, že Linley toto jen třeba mylně předpokládá na základě minulosti, ale pokud má pravdu, tak by toto asi byla ta lepší varianta. I odhlédneme-li od případných sympatií (a důvěry) k Tchajwanu v kontrastu s komunistickou Čínou, by to mohlo mít jednu velkou výhodu: hardware VIA byl přece jen o něco lépe sehnatelný zde na Západě.

Na firmě VIA (nebo Zhaoxinu, pokud se Linley Group mýlí) by tak také bylo vybrat finální jméno. Označení Centaur CHA je patrně jen interní/provizorní, pod značkou VIA by bylo zvoleno nějaké jiné, ať už třeba značka starší jména Nano, Eden, nebo něco úplně nového.

I kvůli těmto otázkám je tedy poněkud skryto v mlze, jaký potenciál představuje nový procesor navržený Centaurem na trhu. Těžko říct, kdy přesně vyjde a zda se bude dát běžně koupit. Zhaoxiny se snad dají sehnat jen v Číně a i ta VIA zase měla poněkud úzkou distribuci spíš jen pro Embedded trh. Zda se tyto procesory a desky pro ně třeba někdy objeví v našich obchodech, je proto hodně nejisté.